PCIe 6.x IP

Filter

Compare

42

IP

from

6

vendors

(1

-

10)

-

PCIe Controller IP

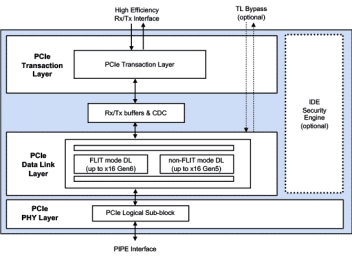

- The PCI Express® (PCIe®) Controller IP is a highly configurable, performance-optimized core designed for ASIC and FPGA integration.

- Supporting PCIe Gen1 through Gen6 at data rates up to 64 GT/s, the controller accommodates a wide range of link widths (x1–x16) and protocol features to meet the demands of next-generation SoC, networking, and high-performance computing platforms.

- The controller seamlessly interoperates with PIPE-compliant PHYs and supports multiple modes including Root Complex, Endpoint, Switch, and Dual-Mode operation.

-

PCIe Gen 6 controller IP

- Designed to the latest PCI Express 6.0 (64 GT/s), 5.0 (32 GT/s), 4.0 (16 GT/s), 3.1/3.0 (8 GT/s), and PIPE 6.x (8, 16, 32, 64 and 128-bit) specifications

- Supports SerDes Architecture PIPE 10b/20b/40b/80b width

- Supports original PIPE 8b/16b/32b/64b/128b width

-

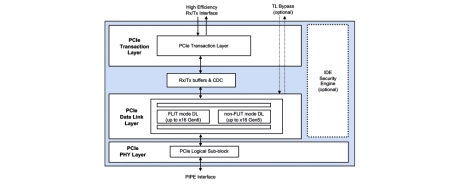

PCIe 6.1 Controller with AXI

- The PCI Express® (PCIe®) 6.1 Controller with AXI is configurable and scalable controller IP designed for ASIC implementation.

- The controller supports the PCIe 6.1 specification, including 64 GT/s data rates, PAM4 signaling, FLIT mode, and L0p power state.

-

PCIe 6.0 (Gen6) Premium Controller with AMBA bridge and LTI & MSI Interfaces

- Supports all required features of the PCI Express 6.2/6.1/6.0.1 (64GT/s), 5.0 (32 GT/s), 4.0 (16 GT/s), 3.1 (8 GT/s) and PIPE (32-bit) specifications

- Based on silicon-proven PCIe 6.x controller design

- Allows a full 64GT/s x16 lane bandwidth with up to 1024-bit data path implementations

- Supports advanced RAS data protection features including ECC

-

PCIe 6.0 (Gen6) Premium Controller with AMBA bridge

- Supports all required features of the PCI Express 6.2/6.1/6.0.1 (64GT/s), 5.0 (32 GT/s), 4.0 (16 GT/s), 3.1 (8 GT/s) and PIPE (32-bit) specifications

- Based on silicon-proven PCIe 6.x controller design

- Allows a full 64GT/s x16 lane bandwidth with up to 1024-bit data path implementations

- Supports advanced RAS data protection features including ECC

-

PCIe 6.0 (Gen6) Premium Controller

- Supports all required features of the PCI Express 6.2/6.1/6.0.1 (64GT/s), 5.0 (32 GT/s), 4.0 (16 GT/s), 3.1 (8 GT/s) and PIPE (32-bit) specifications

- Based on silicon-proven PCIe 6.x controller design

- Allows a full 64GT/s x16 lane bandwidth with up to 1024-bit data path implementations

- Supports advanced RAS data protection features including ECC

-

Adds security Interfaces, features to PCIe 6.0 Premium controllers (Gen6)

- Supports all required features of the PCI Express 6.2/6.1/6.0.1 (64GT/s), 5.0 (32 GT/s), 4.0 (16 GT/s), 3.1 (8 GT/s) and PIPE (32-bit) specifications

- Based on silicon-proven PCIe 6.x controller design

- Allows a full 64GT/s x16 lane bandwidth with up to 1024-bit data path implementations

- Supports advanced RAS data protection features including ECC

-

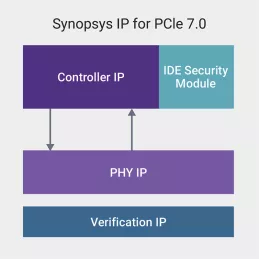

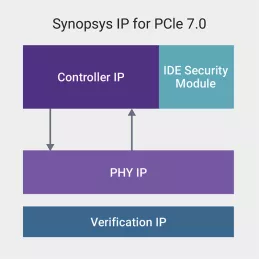

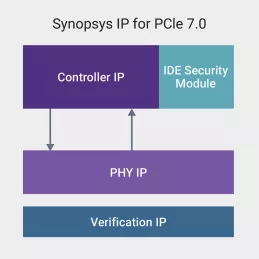

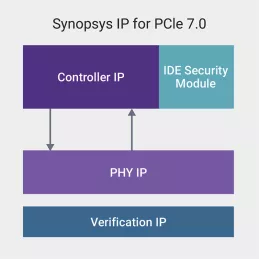

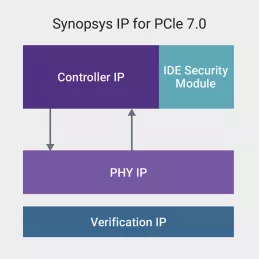

PCIe 6.0 Integrity and Data Encryption Security Module

- Compliant with PCI Express IDE specification

- Support for TDISP

- High-performance AES-GCM based packet encryption, decryption, authentication

- Seamless integration with Synopsys controllers via TLP packet-based interface

- FLIT mode support

-

PCIe 6.0 PHY, TSMC N6 x2 1.2V, North/South (vertical) poly orientation

- Supports the latest features of PCIe 6.x and CXL 3.x specifications

- Supports PAM-4 signaling and up to x16 lane configurations with bifurcation

- Delivers more power efficiency across channels with unique DSP algorithms

- Enables near zero link downtime with patent-pending diagnostic features