PCIe 7.0 IP

Filter

Compare

19

IP

from

7

vendors

(1

-

10)

-

PHY for PCIe 7.0 and CXL

- Architecture optimized for HPC, AI/ML, storage, and networking

- Ultra-long reach, low latency, and low power

- Advanced DSP delivers unmatched performance and reliability

- Comprehensive real-time diagnostic, monitor, and test features

- Bifurcation support for x1, x2, x4, x8, and x16 lanes

-

PCIe 7.0 PHY, TSMC N5 x4, North/South (vertical) poly orientation

- Supports the latest features of PCIe® 7.0 specification

- Supports PAM-4 signaling and up to x16 lane configurations with bifurcation

- Unique DSP algorithms deliver more power efficiency across channels

- Patent-pending diagnostic features enable near zero link downtime

-

PCIe 7.0 PHY, TSMC N3P x4, North/South (vertical) poly orientation

- Supports the latest features of PCIe® 7.0 specification

- Supports PAM-4 signaling and up to x16 lane configurations with bifurcation

- Unique DSP algorithms deliver more power efficiency across channels

- Patent-pending diagnostic features enable near zero link downtime

-

PCIe 7.0 PHY, TSMC N2P x4, North/South (vertical) poly orientation

- Supports the latest features of PCIe® 7.0 specification

- Supports PAM-4 signaling and up to x16 lane configurations with bifurcation

- Unique DSP algorithms deliver more power efficiency across channels

- Patent-pending diagnostic features enable near zero link downtime

-

PCIe 7.0 PHY, TSMC Intel 18A x4, North/South (vertical) poly orientation

- Supports the latest features of PCIe® 7.0 specification

- Supports PAM-4 signaling and up to x16 lane configurations with bifurcation

- Unique DSP algorithms deliver more power efficiency across channels

- Patent-pending diagnostic features enable near zero link downtime

-

PCIe 7.0 PHY in TSMC (N5, N3P)

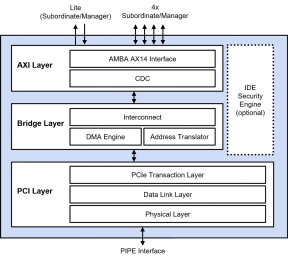

- Physical Coding Sublayer (PCS) block with PIPE interface

- Supports PCIe 7.0, encoding, backchannel initialization

- Lane margining at the receiver

- Spread-spectrum clocking (SSC)

-

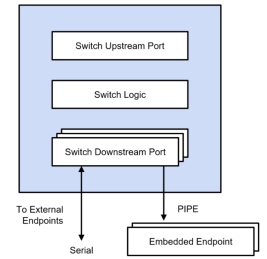

PCIe 7.0 Switch

- Configurable from PCIe 7.0 x8/ PCIe6x16 @1GHz clock down to PCIe 5.0 x1

- Highly scalable with up to 31 configurable external or embedded endpoints

- Configurable Egress Buffer for non-blocking output queueing switch performance

- Flit mode to non-Flit mode conversion

- Low power optimized

- Superior performance through a nonblocking architecture

- Minimized footprint

-

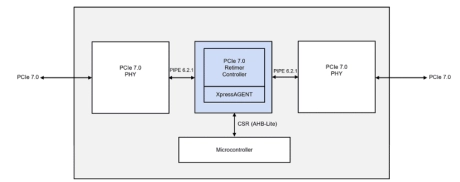

PCIe 7.0 Retimer Controller with CXL Support

- Supports PCIe 7.0 128 GT/s speeds at up to x16 lanes

- CXL 3.0 aware

- Supports PIPE 6.2.1 compatible PHYs

- Optimized for low latency

- Highly-configurable equalization algorithms and adaptive behaviors

-

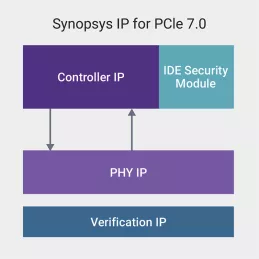

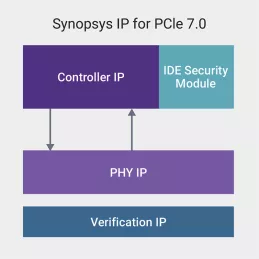

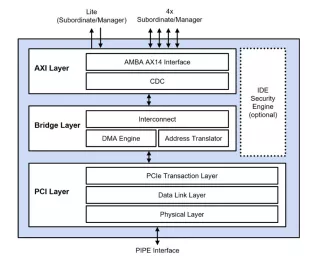

PCIe 7.0 Controller with AXI

- Optimized for high-bandwidth efficiency at data rates up to 128 GT/s

- Separate native TX/RX data path separating posted/Non posted/completion traffic

- Handles up to 4 TLPs per cycle

- Advanced PIPE modes and port bifurcation

-

PCIe 7.0 Controller

- Optimized for high-bandwidth efficiency at data rates up to 128 GT/s

- Separate native TX/RX data path separating posted/Non posted/completion traffic

- Handles up to 4 TLPs per cycle

- Advanced PIPE modes and port bifurcation