Motion JPEG IP

Filter

Compare

23

IP

from

6

vendors

(1

-

10)

-

Motion JPEG Encoder

- Supports Xilinx® Zynq®-7000 AP SoC and 7 series FPGA families

- Compliant with the Baseline Sequential DCT mode of the ISO/IEC 10918-1 JPEG standard

-

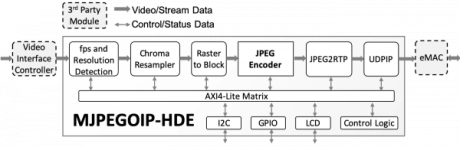

Motion JPEG Over IP – HD Video Encoder Subsystem

- This Video Over IP Subsystem employs JPEG compression and RTP/UDP/IP encapsulation to enable the rapid development of complete motion JPEG video streaming products. Hardware reference designs and customization services complete the solution.

- The subsystem uses CAST’s JPEG-E-S, JPEG2RTP, and UDPIP IP cores.

-

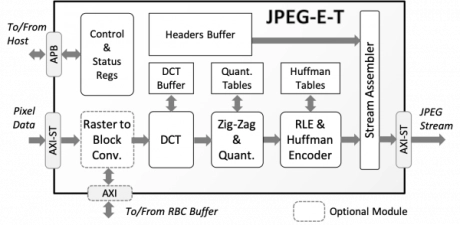

Tiny Baseline JPEG Encoder

- This JPEG compression IP core supports the Baseline Sequential DCT and the Extended Sequential DCT modes of the ISO/IEC 10918-1 standard.

- It implements an area-efficient, hardware JPEG encoder with very low processing latency.

- Probably the smallest JPEG encoder IP core in the market, the JPEG-E-T occupies about 40,000 equivalent NAND2 gates.

-

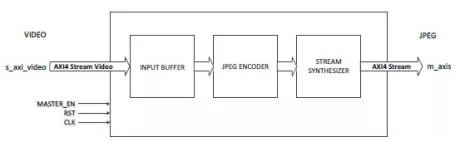

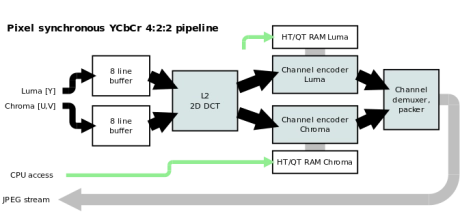

JPEG encoder

- Baseline JPEG compliant (ITU T.81), Motion JPEG

- Up to 12 bits depth possible (default: 8 bit)

- Super low latency (less than 1/10 of frame duration for rolling shutter cameras)

- Lossy compression by default

- Fully bit and cycle accurate co-simulation model available in Docker container

-

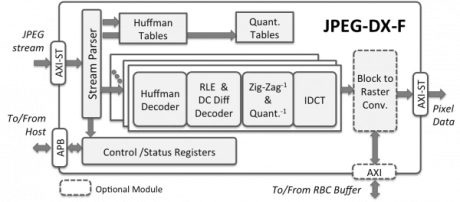

Ultra-Fast Baseline and Extended JPEG Decoder

- This JPEG decompression IP core supports the Baseline Sequential DCT and Extended Sequential DCT modes of the ISO/IEC 10918-1 standard.

- It implements a scalable, ultra-high-performance, ASIC or FPGA, hardware JPEG decoder that handles extremely high pixel rates.

-

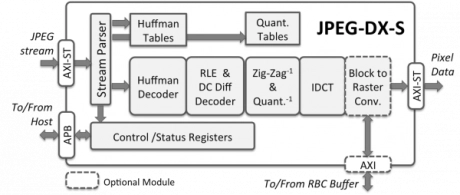

Baseline and Extended JPEG Decoder

- The JPEG-DX-S IP core is an area-efficient, high-performance JPEG decoder conforming to the Baseline Sequential DCT and the Extended Sequential DCT modes of the ISO/IEC 10918-1 standard.

- It decompresses JPEG images, and also video payload for Motion-JPEG container formats.

-

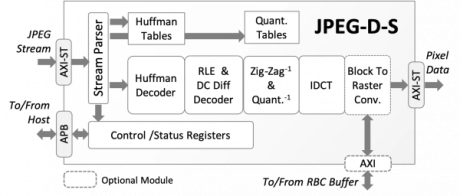

Baseline JPEG Decoder

- This JPEG decompression IP core supports the Baseline Sequential DCT mode of the ISO/IEC 10918-1 standard. It implements a high-performance hardware JPEG decoder that is very small in silicon area.

- The JPEG-D-S Decoder decompresses JPEG images and the video payload for Motion-JPEG container formats.

-

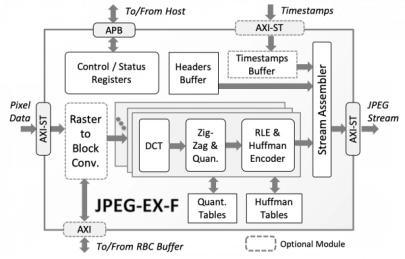

Ultra-Fast Baseline and Extended JPEG Encoder

- This JPEG compression IP core supports the Baseline Sequential DCT and the Extended Sequential DCT modes of the ISO/IEC 10918-1 standard.

- It implements a scalable, ultra-high-performance, ASIC or FPGA, hardware JPEG encoder that can compress high pixel rate video using significantly fewer silicon resources and less power than encoders for video compression standards such as HEVC/H,265, DSC, AVC/H.264, or JPEG200.

-

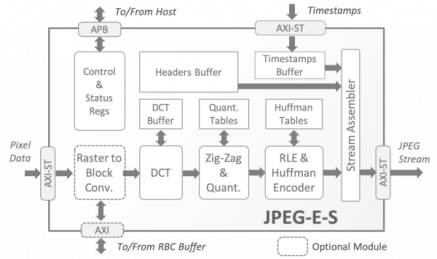

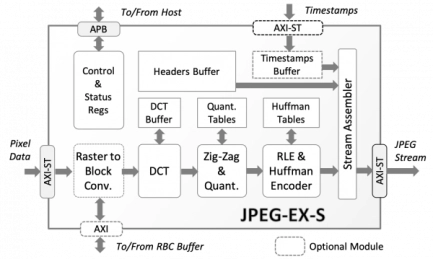

Baseline and Extended JPEG Encoder

- This JPEG compression IP core supports the Baseline Sequential DCT and Extended Sequential DCT modes of the ISO/IEC 10918-1 standard.

- It implements an area-efficient, high-performance, ASIC or FPGA hardware JPEG encoder with very low processing latency.

-

Baseline JPEG Encoder

- This JPEG compression IP core supports the Baseline Sequential DCT modes of the ISO/IEC 10918-1 standard. It implements an area-efficient, high-performance, hardware JPEG encoder with remarkably low processing latency.

- The JPEG-E-S encoder produces compressed JPEG images and the video payload for Motion-JPEG container formats. It accepts images with 8-bit color samples and up to four color components, in all widely-used color subsampling formats.