MIPI D-PHY RX+ IP

Filter

Compare

293

IP

from

28

vendors

(1

-

10)

-

MIPI D-PHY RX+ (Receiver) IP

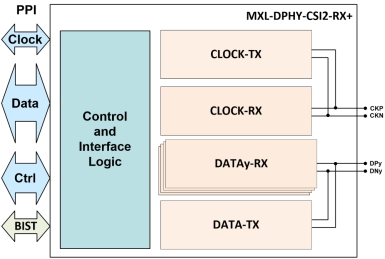

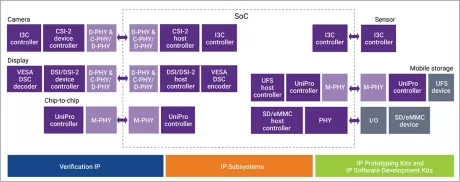

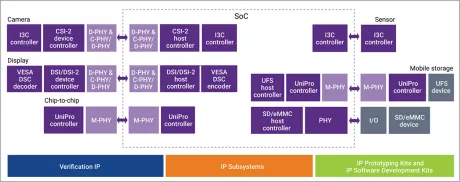

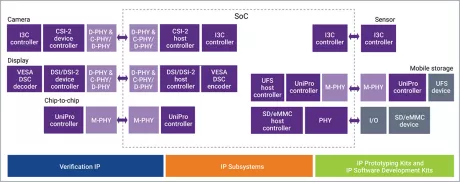

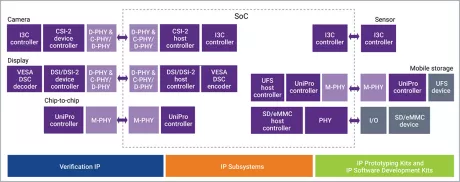

- The MIPI® D-PHY RX+ is a proprietary implementation of the MIPI Camera Serial Interface 2 (CSI-2) and Display Serial Interface (DSI) D-PHY Receiver.

- It is optimized to achieve full-speed production testing, in-system testing, and higher performance compared to traditional configurations, while reducing area and standby power.

-

MIPI DPHY Rx 2 Lanes - UMC 28HPC 1.8V, North/South Poly Orientation

- Compliant with the MIPI D-PHY specification, v1.2

- Fully integrated hard macro

- Up to 2.5 Gbps per lane

- Aggregate throughput up to 10 Gbps in 4 data lanes

-

MIPI DPHY Rx 4 Lanes - UMC 22ULP 1.8V, North/South Poly Orientation

- Compliant with the MIPI D-PHY specification, v1.2

- Fully integrated hard macro

- Up to 2.5 Gbps per lane

- Aggregate throughput up to 10 Gbps in 4 data lanes

-

MIPI D-PHY Rx 4 Lanes - TSMC7FF18, North/South Poly Orientation

- Compliant with the MIPI D-PHY specification, v1.2

- Fully integrated hard macro

- Up to 2.5 Gbps per lane

- Aggregate throughput up to 10 Gbps in 4 data lanes

-

MIPI D-PHY Rx 2 Lanes - TSMC7FF18, North/South Poly Orientation

- Compliant with the MIPI D-PHY specification, v1.2

- Fully integrated hard macro

- Up to 2.5 Gbps per lane

- Aggregate throughput up to 10 Gbps in 4 data lanes

-

MIPI D-PHY Rx 4 Lanes - TSMC6ff18, North/South Poly Orientation

- Compliant with the MIPI D-PHY specification, v1.2

- Fully integrated hard macro

- Up to 2.5 Gbps per lane

- Aggregate throughput up to 10 Gbps in 4 data lanes

-

MIPI D-PHY Rx 2 Lanes - TSMC6ff18, North/South Poly Orientation

- Compliant with the MIPI D-PHY specification, v1.2

- Fully integrated hard macro

- Up to 2.5 Gbps per lane

- Aggregate throughput up to 10 Gbps in 4 data lanes

-

MIPI D-PHY Rx 4 Lanes - TSMC40ULP25

- Compliant with the MIPI D-PHY specification, v1.2

- Fully integrated hard macro

- Up to 2.5 Gbps per lane

- Aggregate throughput up to 10 Gbps in 4 data lanes

-

MIPI D-PHY Rx 2 Lanes - TSMC40ULP25

- Compliant with the MIPI D-PHY specification, v1.2

- Fully integrated hard macro

- Up to 2.5 Gbps per lane

- Aggregate throughput up to 10 Gbps in 4 data lanes

-

MIPI D-PHY Rx 4 Lanes - TSMC12FFC18, North/South Poly Orientation

- Compliant with the MIPI D-PHY specification, v1.2

- Fully integrated hard macro

- Up to 2.5 Gbps per lane

- Aggregate throughput up to 10 Gbps in 4 data lanes