MIPI C-PHY/D-PHY Combo IP

Filter

Compare

45

IP

from

6

vendors

(1

-

10)

-

MIPI C-PHY/D-PHY Combo IP

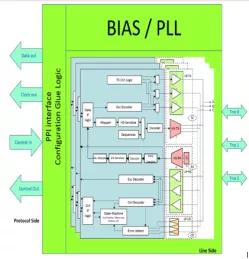

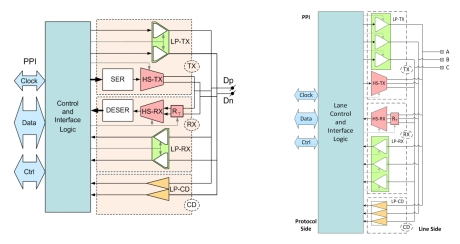

- The MIPI C/D-PHY combo IP is a high-frequency low-power, low cost, physical layer compliant with the MIPI® Alliance Standard for C-PHY and D-PHY.

- The PHY can be configured as a MIPI Master or MIPI Slave, supporting camera interface CSI-2 v1.2 or display interface DSI v1.3 applications in the D-PHY mode. It also supports camera interface CSI-2 v1.3 and display interface DSI-2 v1.0 applications in the C-PHY mode.

-

MIPI C-PHY/D-PHY combo Rx

- MIPI C-PHY v2.0 up to 6.5 Gbps

- 3 trio configuration

- MIPI D-PHY v2.1 up to 6.5Gbps

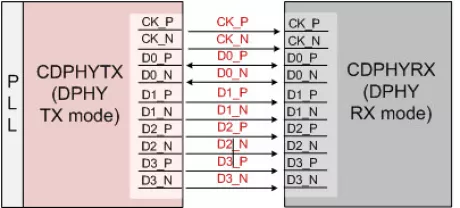

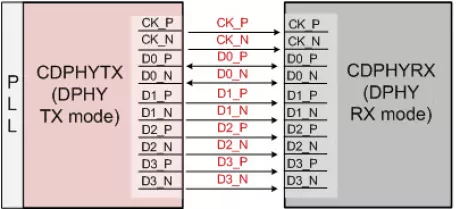

- 4D-1C configuration

-

MIPI C-PHY/D-PHY Combo v1.2 IP in TSMC(5nm, 7nm, 12/16nm, 28nm and 40nm)

- Fully compliant with MIPI D-PHY v1.2 and C-PHY v1.0 spec

- Supports MIPI CSI-2 protocol

-

MIPI C/D Combo PHY RX - GlobalFoundries 22FDX

- Supports up to one clock lane and four data lanes for DPHY1.2

- Fully compliant with MIPI D-PHY v1.2 and C-PHY v1.0 spec

- Available in GlobalFoundries 22FDX process

- Three 3phase encoded data lanes for CPHY1.0

-

MIPI C/D Combo PHY TX

- Supports HS TX data rate up to 2.5Gbps (2.5Gsps) per lane (trio)

- Fully compliant with MIPI D-PHY v1.2 and C-PHY v1.0 spec

- Available in GlobalFoundries 22FDX process

- Three 3phase encoded data lanes for CPHY1.0

-

MIPI C/D-PHY Combo Rx IP, Silicon Proven in TSMC 40 LP

- Compliant with MIPI D-PHY spec up to v2.5 and C-PHY spec up to v2.0

- Support both MIPI DSI and CSI-2 protocols

- Support HS data rate up to 6Gbps ( 6Gsps ) per lane (per trio)

- Support LS data rate of 10Mbps and Ultra-low power mode

-

MIPI C/D-PHY Combo Tx IP, Silicon Proven in TSMC 40 LP

- Compliant with MIPI D-PHY spec up to v2.5 and C-PHY spec up to v2.0

- Support both MIPI DSI and CSI-2 protocols

- Support HS data rate up to 6Gbps ( 6Gsps ) per lane (per trio)

- Support LS data rate of 10Mbps and Ultra-low power mode

-

MIPI C/D-PHY Combo Rx IP, Silicon Proven in TSMC 28 HPC+

- Compliant with MIPI D-PHY spec up to v2.5 and C-PHY spec up to v2.0

- Support both MIPI DSI and CSI-2 protocols

- Support HS data rate up to 6Gbps ( 6Gsps ) per lane (per trio)

- Support LS data rate of 10Mbps and Ultra-low power mode

-

MIPI C/D-PHY Combo Tx IP, Silicon Proven in TSMC 28 HPC+

- Compliant with MIPI D-PHY spec up to v2.5 and C-PHY spec up to v2.0

- Support both MIPI DSI and CSI-2 protocols

- Support HS data rate up to 6Gbps ( 6Gsps ) per lane (per trio)

- Support LS data rate of 10Mbps and Ultra-low power mode

-

MIPI C/D-PHY Combo Rx IP, Silicon Proven in TSMC 22 ULP

- Compliant with MIPI D-PHY spec up to v2.5 and C-PHY spec up to v2.0

- Support both MIPI DSI and CSI-2 protocols

- Support HS data rate up to 6Gbps ( 6Gsps ) per lane (per trio)

- Support LS data rate of 10Mbps and Ultra-low power mode