MIPI C-PHY IP

Filter

Compare

197

IP

from

22

vendors

(1

-

10)

-

MIPI CPHY v1.1 Analog Interface

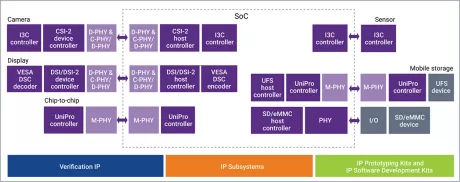

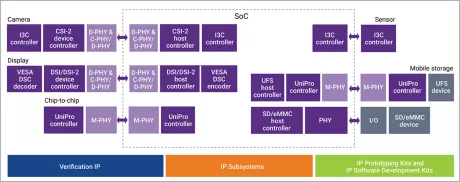

- The MIPI CPHY V1.1 improves throughput over a bandwidth-limited channel, allowing more data without an increased signaling clock.

- It is intended to be used for camera interface (CSI-2 v1.3) and display interface (DSI-2 v1.0).

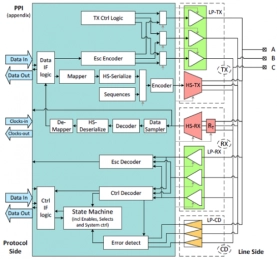

- The signaling interface uses a 3-phase transceiver that encodes 3-bit symbols over 3 wires. This is different from the two-wire differential “lane” used in D-PHY.

-

MIPI C-PHY

- Physical interface for CSI-2 providing 5.7Gbps per lane of bandwidth The MIPI C-PHY V1.0 improves throughput over a bandwidth-limited channel, allowing more data without increased signaling clock.

-

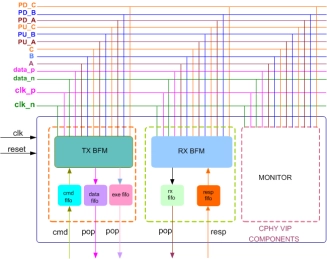

MIPI CPHY Verification IP

- Full MIPI CPHY Transmitter and Receiver functionality.

- Supports 2.0 MIPI CPHY Specifications.

- Supports up to 32 trio lanes.

- Supports both serial and PPI functionality testing.

-

MIPI C-PHY v1.2 D-PHY v2.1 RX 3 trios/4 Lanes - TSMC7FF 1.8V, North/South Poly Orientation

- Compliant with the MIPI D-PHY specification, v2.1

- 4 Lanes in D-PHY mode up to 6.5Gb/s per lane

- Compliant with the MIPI C-PHY specification, v2.0

- 3 trios in C-PHY mode up to 6.5Gs/s per trio

-

MIPI C-PHY v1.2 D-PHY v2.1 TX 3 trios/4 Lanes - TSMC7FF 1.8V, N/S, for Automotive, ASIL B Random, AEC-Q100 Grade 2

- Compliant with the MIPI D-PHY specification, v2.1

- 4 Lanes in D-PHY mode up to 6.5Gb/s per lane

- Compliant with the MIPI C-PHY specification, v2.0

- 3 trios in C-PHY mode up to 6.5Gs/s per trio

-

MIPI C-PHY v1.2 D-PHY v2.1 TX 3 trios/4 Lanes - TSMC6FFC 1.8V, North/South Poly Orientation

- Compliant with the MIPI D-PHY specification, v2.1

- 4 Lanes in D-PHY mode up to 6.5Gb/s per lane

- Compliant with the MIPI C-PHY specification, v2.0

- 3 trios in C-PHY mode up to 6.5Gs/s per trio

-

MIPI C-PHY v1.2 D-PHY v2.1 RX 3 trios/4 Lanes - TSMC6FF 1.8V, North/South Poly Orientation

- Compliant with the MIPI D-PHY specification, v2.1

- 4 Lanes in D-PHY mode up to 6.5Gb/s per lane

- Compliant with the MIPI C-PHY specification, v2.0

- 3 trios in C-PHY mode up to 6.5Gs/s per trio

-

MIPI C-PHY v1.2 D-PHY v2.1 TX 3 trios/4 Lanes - TSMC16FFC 1.8V, North/South Poly Orientation

- Compliant with the MIPI D-PHY specification, v2.1

- 4 Lanes in D-PHY mode up to 6.5Gb/s per lane

- Compliant with the MIPI C-PHY specification, v2.0

- 3 trios in C-PHY mode up to 6.5Gs/s per trio

-

MIPI C-PHY v1.2 D-PHY v2.1 TX 2 trios/2 Lanes - TSMC16FFC 1.8V, North/South Poly Orientation

- Compliant with the MIPI D-PHY specification, v2.1

- 4 Lanes in D-PHY mode up to 6.5Gb/s per lane

- Compliant with the MIPI C-PHY specification, v2.0

- 3 trios in C-PHY mode up to 6.5Gs/s per trio

-

MIPI C-PHY v1.2 D-PHY v2.1 RX 3 trios/4 Lanes - TSMC16FFC 1.8V, North/South Poly Orientation

- Compliant with the MIPI D-PHY specification, v2.1

- 4 Lanes in D-PHY mode up to 6.5Gb/s per lane

- Compliant with the MIPI C-PHY specification, v2.0

- 3 trios in C-PHY mode up to 6.5Gs/s per trio