MDDI IP

Filter

Compare

3,208

IP

from

244

vendors

(1

-

10)

-

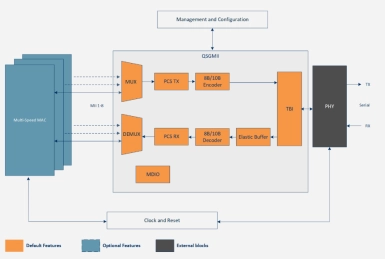

Quad Serial Gigabit Media Independent Interface (QSGMII)

- QSGMII (Quad Serial Gigabit Media Independent Interface) IP from Comcores is a high-speed serial interface developed to aggregate four Gigabit Ethernet (SGMII) ports into a single high-speed serial link using 8b/10b encoding at 5 Gbps.

- It reduces the number of physical connections needed between Ethernet MACs and PHYs contributing to lowering power and cost.

-

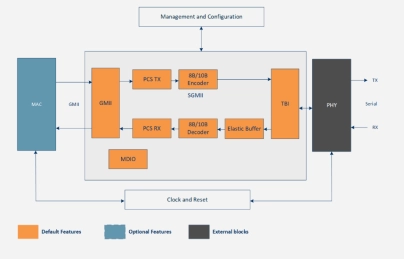

Serial Gigabit Media Independent Interface (SGMII)

- SGMII (Serial Gigabit Media Independent Interface) IP is a high-speed serial interface developed to connect a Gigabit Ethernet MAC (Media Access Controller) to a PHY (Physical Layer Device).

- It reduces the number of physical connections needed between Ethernet MACs and PHYs contributing to lowering power and cost.

-

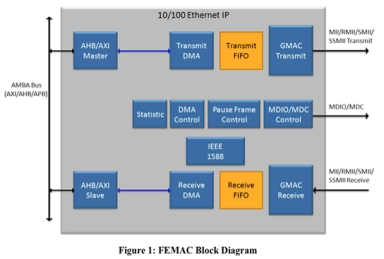

Fast Ethernet Media Access Controller

- The Fast Ethernet Media Access Controller (FEMAC) with AHB or AXI Interface core incorporates the essential protocol requirements for operation of 10/100 Mbps Ethernet/IEEE 802.3-2008 compliant node, and provides interface between the AHB or AXI Interface and the Media Independent Interface (MII) for the Ethernet operation.

- Optionally the core supports RMII (Reduced MII Interface) and SMII (Serial MII Interface) for reducing the pin count to interface with external PHY device.

-

Media Access Control Security (MACSec)

- Up to four ports of concurrent traffic with an aggregate bandwidth of 100G are supported by one core (1x100G, 2x50G, 2x40G, 4x25G, 4x10G, 4x1G, 1x50G+2x25G)

- Line rate operation

- Flexible control/non-control port filtering

- Configurable number of Secure Channels (SCs) and Security Associations (SAs) per physical port

-

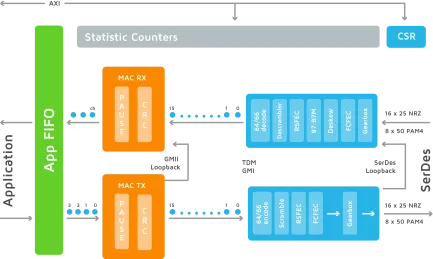

Multi-channel, multi-speed Ethernet universal media access control (MAC) and physical coding sublayer IP (UMAC)

- Programmable application-side FIFO sizes (or complete bypass ) on TX, RX or both for easy integration with application logic

- Packing and unpacking logic for application to internal data path matching

- Supports line rate with minimum IFG

- Memory-based statistics counter implementation for Area/gate savings

-

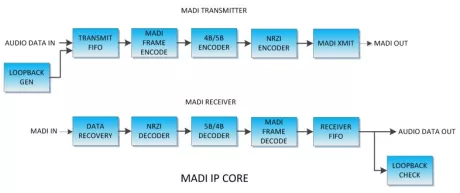

Multi-channel Audio Digital Interface (MADI) IP Core

- No high-speed transceivers required (Hotlink or other)

- Built-in loopback mode with data generation and testing

- Can be configured for number of channels

- Generic FIFO interfaces are provded for the user side interface

-

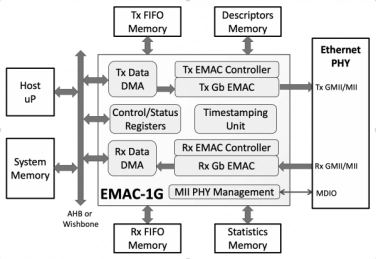

Gigabit Ethernet Media Access Controller

- Implements an Ethernet Media Access Controller compatible with the 10/100 Mbps IEEE 802.3 and 1Gbps IEEE 802.3-2002 specifications.

- The controller provides half- or full-duplex operation, supports jumbo frames, and optionally provides a useful set of statistics counters enabling station management.

- Furthermore, the core can optionally be configured with a hardware timestamping unit enabling support for the IEEE 1588 precision time protocol (PTP).

-

10/100 Mb Media Access Controller with RMII

- Conforms to IEEE 802.3-2002 specification

- Configurable width CPU interface with little or big endianess:

- Simple interface allows easy connection to CPU

- Narrow address bus (4 bits) with indirect I/O interface for transmitted and received data dual port memories

-

Media Local Bus Interface

- Adds MOST® connectivity to Xilinx® FPGAs

- Licensed MediaLB® technology from SMSC®

- Compliant with the MLB Specification Version 4.2

- Supports 3-pin and 6-pin interface to INICs

-

Reduced Media Independent Interface (RMII)

- Option to specify fixed 10 or 100 Mbit per second throughput

- Automatic detection of Receive side throughput

- Fixed clock frequency of 50 MHz Designed to RMII Consortium specification

- Free core provided with the Embedded Development Kit (EDK)