Low-Noise Linear Regulator IP

Filter

Compare

5

IP

from

2

vendors

(1

-

5)

-

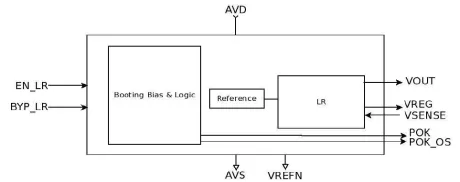

Linear regulator, low-noise optimized for sensitive analog loads such as CODEC and Reference

- Starring a PSRR of -65 dB at 20 kHz and a low intrinsic noise, combined with a low quiescent current of 110 uA, the nLR-VAIPO helps optimize the power management network for audio handheld applications such as smartphone and tablet.

- Small footprint: only 0.12 mm2 (including bandgap reference and POK circuit)

- Minimization of the overall system power, through the support of 3 modes of operation: normal, shutdown and bypass

- Eases integration in SoC nLR-VAIPO is delivered with behavioral models. These new views enable to build an optimized Power Management Network (PMNet) by verifying mode transitions as well as noise propagation.

-

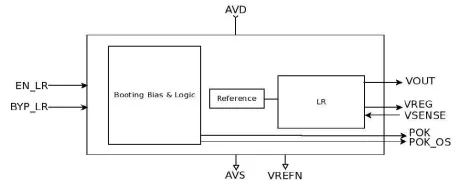

Linear regulator, low-noise optimized for sensitive analog loads such as CODEC and Reference

- Starring a PSRR of -65 dB at 20 kHz and a low intrinsic noise, combined with a low quiescent current of 110 uA, the nLR-VAIPO helps optimize the power management network for audio handheld applications such as smartphone and tablet.

- Small footprint: only 0.12 mm2 (including bandgap reference and POK circuit)

- Minimization of the overall system power, through the support of 3 modes of operation: normal, shutdown and bypass

- Eases integration in SoC nLR-VAIPO is delivered with behavioral models. These new views enable to build an optimized Power Management Network (PMNet) by verifying mode transitions as well as noise propagation.

-

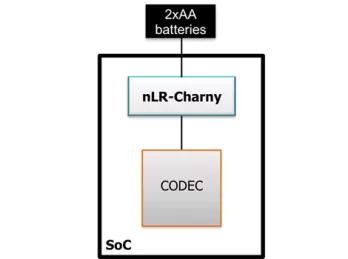

Linear Regulator, Low-noise optimized for sensitive application such as RF or PLL blocks

- Low noise: high power Supply Rejection Ratio (PSRR): - 65 dB at F < 10 kHz

- Low intrinsic noise: 20 uVRMS at 10 Hz to 20 kHz

- Low Bill-of-Material: optimized in density for the best trade-off for the given output current and input voltage range

- Cost efficient solution compared to external Power Management.

-

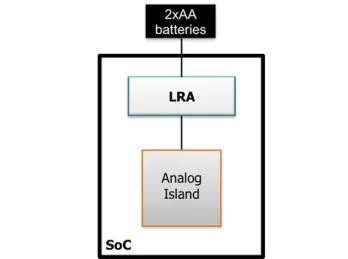

Linear Regulator for analog island

- Low-noise enhancement

- Power Supply Rejection Ratio: - 50 at F≤ 10kHz

- Output Noise: 30 u VRMS at IOUT = IMAX

- Low Dropout Voltage: 107.3 mV

-

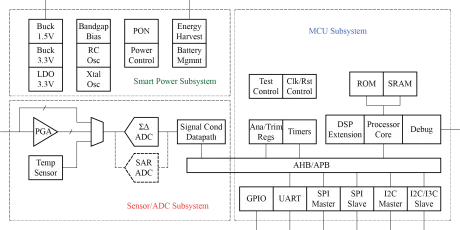

Intelligent Sensor and Power Management Design Platform

- Smart Power Subsystem

- Sensor AFE

- MCU Subsystem