LIN Controller IP

Filter

Compare

14

IP

from

9

vendors

(1

-

10)

-

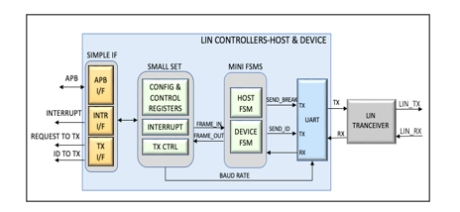

Host / device LIN controller IP

- The LIN Controllers IP– Local Interconnect Network Controllers IPs are compliant to LIN 2.0, 2.1 & 2.2A Specifications. Backward compliant to LIN 1.3 Specification as well.

- These can be integrated into systems through various simple AMBA-APB, AMBA-AHB or SRAM like interfaces that require LIN connectivity commonly used in automotive and industrial applications.

-

LIN Controller IIP

- Compliant with 2.2A LIN Specification

- Full LIN transmit and receive functionality

- Supports configurable master or slave functionality

- Supports all frame types

-

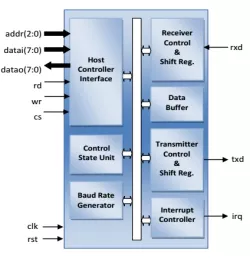

Local Interconnect Network (LIN) Soft Controller IP

- Conforms with LIN 1.3, LIN 2.1 and LIN 2.2 specification.

- Automatic LIN Header handling

- Automatic Re-synchronization

- Data rate between 1Kbit/s and 20 Kbit/s

-

LIN 2.2, 2.1 and 1.3 Protocol Controller IP

- Conforms with LIN 1.2, LIN 2.1 and LIN 2.2 specification.

- Automatic LIN Header handling

- Automatic Re-synchronization

- Data rate between 1Kbit/s and 20 Kbit/s

-

LIN Bus Controller – Basic and Safety-Enhanced

- Conforms with LIN 1.2, LIN 2.1 and LIN 2.2 specification.

- Automatic LIN Header handling

- Automatic Re-synchronization

- Data rate between 1Kbit/s and 20 Kbit/s

-

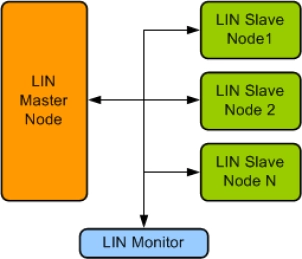

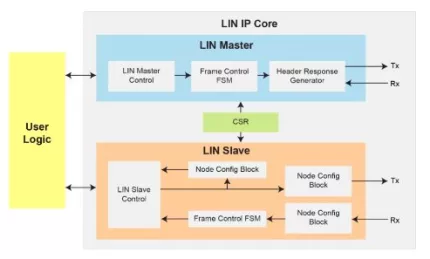

LIN Master Slave Controller

- LIN is a single wire-based interface, it reduces the cost and complexity of implementation.

- LIN is the best-suited and best alternative to CAN for applications that do not need high Bandwidth and that are of low speed.

- LIN is self-synchronized and therefore no need for external oscillators.

-

LIN Bus Master/Slave Controller

- Support of LIN specifications 2.0, 2.1, and 2.2A

- Backward compatible with LIN specification 1.3

- Run-time configurable master or slave operation

- Programmable data rate between 1 Kbit/s and 20 Kbit/s (for master)

-

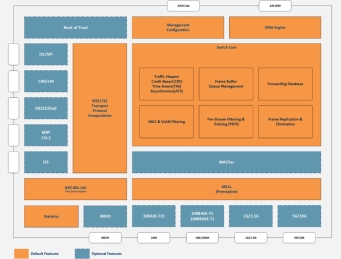

Zonal Controller

- Complete solution that integrates both hardware and software components including a TSN-capable Ethernet switch, a Root of Trust security module, and a transport protocol encapsulation system based on IEEE 1722

-

FlexRay Controller

- Flexray is more reliable compared to CAN, LIN.

- Flexray is more faster compared to CAN, LIN.

- High data rates.

-

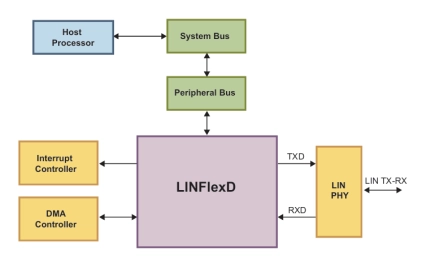

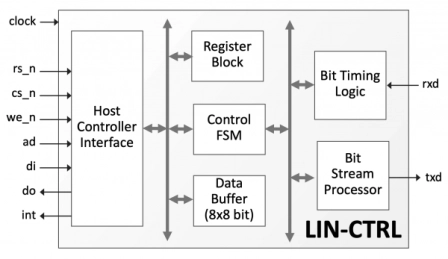

LINFlexD Controller

- The LINFlexD Controller is a serial communication interface designed for Local Interconnect Network (LIN) applications.

- The LINFlexD manages a high number of LIN messages efficiently with a minimum of CPU load.

- The LINFlexD supports LIN protocol versions 1.3, 2.0, 2.1, and 2.2 and provides an 8-byte buffer for transmit/receive data.