H.264 High-Profile Encoder IP

Filter

Compare

33

IP

from

11

vendors

(1

-

10)

-

H.264 Encoder High Profile (8K on Zynq/Arria)

- Video compression standard ITU.T Rec. H.264 | ISO/IEC 14496-10 AVC.

- EXTREME SPEED, providing a constant throughput of >5 pixels encoded per clock cycle.

-

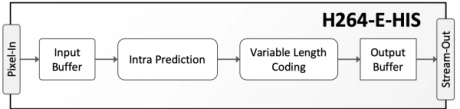

H.264 High 10 Intra Profile Encoder

- The H264-E-HIS IP core is a video encoder compliant to the High 10 Intra profile of the ISO/IEC 14496-10/ITU-T H.264 standard.

- The encoder core has a small silicon footprint—approximately 220K gates and 280K to 420K bits of SRAM—and requires no external memory (e.g. off-chip DRAM) allowing for very cost-effective and low-power ASIC or FPGA implementations.

-

H.264/AVC 4K 60p High Profile Encoder

- - H.264 High Profile(Level1~5.2)

- - Bit rate: up tp 240Mbps

- - Frame rare: up to 60fps

- - Video Formats:YCbCr 4:2:0(1080i/60,

-

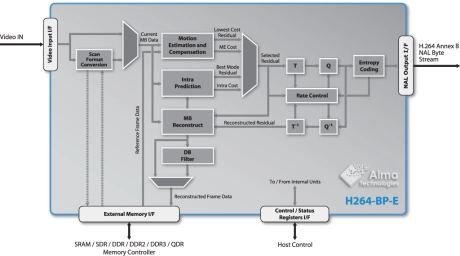

Baseline Profile H.264 Encoder

- The H264-BP-E core is an advanced self-contained hardware H.264 encoder that conforms to the ITU-T H.264 Constrained Baseline Profile.

- This core is available in Intra-only [IDR], Light Motion Estimation [LME] and Full Motion Estimation [FME] prediction engine configurations.

- It supports the real time encoding of both single and multiple 8-bit 4:2:0 video streams, up to Profile Level 5.2.

-

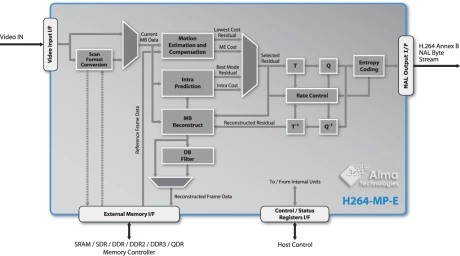

Main Profile H.264 Encoder

- The H264-MP-E core is an advanced self-contained hardware H.264 encoder that conforms to the ITU-T H.264 Main Profile.

- This core is available in Intra-only [IDR], Light Motion Estimation [LME] and Full Motion Estimation [FME] prediction engine configurations.

- It supports the real time encoding of both single and multiple 8-bit 4:2:0 video streams, up to Profile Level 5.2.

-

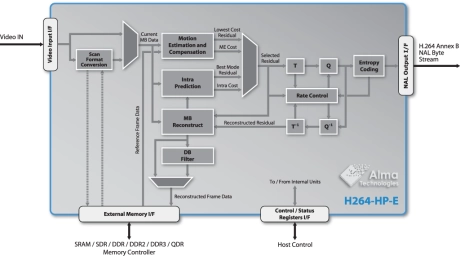

High Profiles H.264 Encoder − High 10, High 4:2:2 and High 4:4:4 (12-bit 4:2:2 or 4:2:0) Profiles

- The H264-HP-E core is an advanced and self-contained ITU-T H.264 High profiles hardware encoder.

- This core is available in Intra-only [IDR], Light Motion Estimation [LME] and Full Motion Estimation [FME] prediction engine configurations.

- It supports real time encoding of both single and multiple 4:2:0 and 4:2:2 video streams, in 8-, 10- or 12-bit per component color depth, up to Profile Level 5.2.

-

High profile 720p@30fps~1080p@240fps

- Output: NAL standard packets

- GOP configuration: I, IP

- I16x16 and I4x4 all intra prediction modes

- Multiple inter prediction modes

-

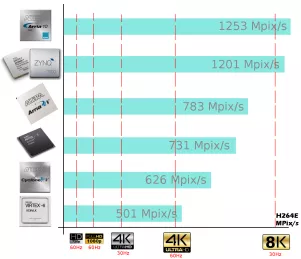

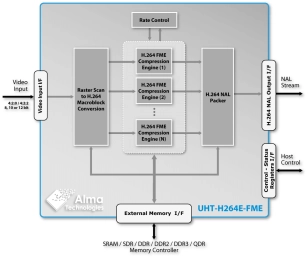

Scalable Ultra-High Throughput H.264 Encoder − Full Motion Estimation

- The UHT-H264E-FME core is a scalable, ultra-high throughput, hardware H.264 encoder, designed to enable 4K and 8K Ultra HD resolutions in power- and cost-effective FPGA or ASIC implementations.

- Powered by a highly-featured Full Motion Estimation engine, this encoder is the most advanced one of our UHT H.264 IP cores and offers best-in-class compression for applications needing advanced H.264 efficiency for high-quality, low-bitrate video encoding.

-

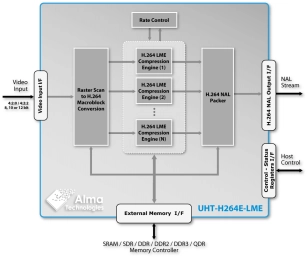

Scalable Ultra-High Throughput H.264 Encoder − Light Motion Estimation

- The UHT-H264E-LME core implements a simple and flexible, requests based, external memory interface with independent read and write data paths.

- The external memory I/F is also designed to be tolerant to memory delays and latencies, which may be present in a shared memory system architecture.

-

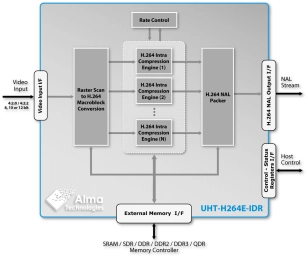

Scalable Ultra-High Throughput H.264 Encoder − Intra Frames (IDR) Encoding

- The UHT-H264E-IDR core implements a simple and flexible, requests based, external memory interface with independent read and write data paths.

- The external memory I/F is also designed to be tolerant to memory delays and latencies, which may be present in a shared memory system architecture.