Ethernet PCS IP

Filter

Compare

312

IP

from

39

vendors

(1

-

10)

-

Ethernet PCS 1G/2.5G/5G/10G/25G & CPRI 7.0

- A combined silicon agnostic implementation of the PCS layer compliant with Ethernet standard IEEE 802.3-2018 and CPRI Specification V7.0 based solution

- The IP-core supports 1G, 2.5G, 5G, 10G, and 25G Ethernet data rates as well as CPRI data rate option 1 (614.14M) to option 10 (24.33024G).

-

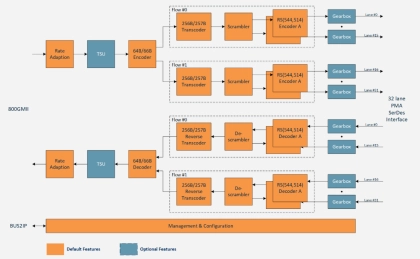

Ethernet PCS 800G

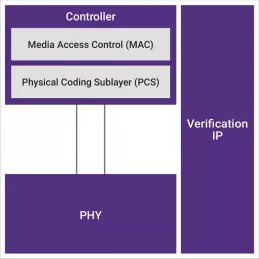

- The 800G Ethernet PCS IP core is a silicon agnostic implementation of the Physical Coding Sublayer (PCS) described in the Ethernet standard IEEE 802.3-2020 and is compliant with Clause 170 and Clause 172 of the IEEE 802.3df specification.

- 800G Ethernet PCS IP provides an interface between the Media Access Control (MAC) and Physical Medium Attachment (PMA) through a 32-lane parallel interface and offers an 800GMII interface on the other side.

-

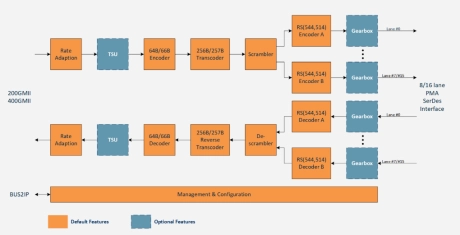

Ethernet PCS 200G/400G

- The 200G/400G Ethernet PCS IP core is a silicon agnostic implementation of the Physical Coding Sublayer (PCS) described in the Ethernet standard IEEE 802.3-2020 and its compliant with Clause 117 and Clause 119 of IEEE 802.3 specification.

- Ethernet PCS 200G/400G IP provides an interface between the Media Access Control (MAC) and Physical Medium Attachment (PMA) through a 8 or 16-lane parallel interface and offers a 200GMII or 400GMII interface on the other side.

-

1.6T Ethernet PCS IP

- Supports all required features of the IEEE 802.3 specification and draft specifications

- IP available in single 1.6T mode and quad channel mode supporting 4 x 400G, 2 x 800G and 1.6T

- Designed to be used with Synopsys 1.6T MAC IP for 1.6T Ethernet Systems

- Includes RS-FEC functions

-

Enterprise Ethernet PCS IP

- Compliant with IEEE standards25G Consortium specifications for 25G & 50G r1.6 (Oct 15, 2015)

- Configurable for 10G, 25G, 40G, 50G and 100G Ethernet applications

- Integration tested with the Synopsys Enterprise Ethernet MAC and Multi-Protocol PHYs

- Comprehensive deliverables packaged in an IP-XACT compatible .run file

-

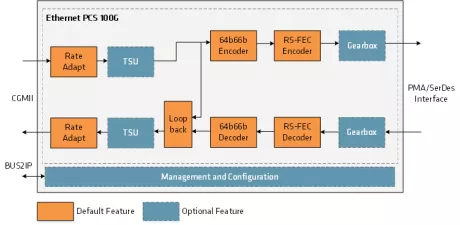

Ethernet PCS 100G

- The Ethernet PCS 100G IP core is a silicon agnostic implementation of the Physical Coding Sublayer (PCS) described in the Ethernet standard IEEE 802.3-2018 and compliant with Clause 82 of IEEE 802.3ba and Clause 91 of IEEE 802.3bj specification.

- The Ethernet PCS 100G IP supports 100G line rates, however other Ethernet PCS speeds are available, such as 1G/2.5G and 10G/25G.

-

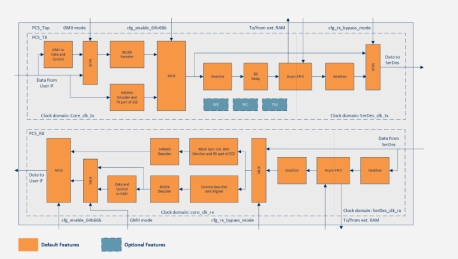

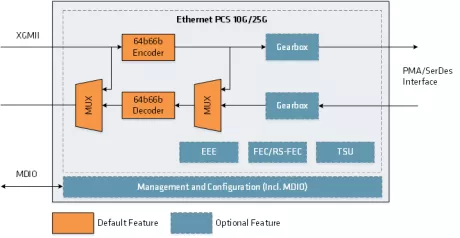

Ethernet PCS 10G/25G

- The Ethernet PCS 10G/25G IP core is a silicon agnostic implementation of the Physical Coding Sublayer (PCS) compliant with Ethernet standard IEEE 802.3-2018 and with Clause 49 of IEEE 802.3ae specification.

- The Ethernet PCS 10G/25G IP supports 10G and 25G line rates, however other Ethernet PCS speeds are available, such as 1G/2.5G and 100G.

-

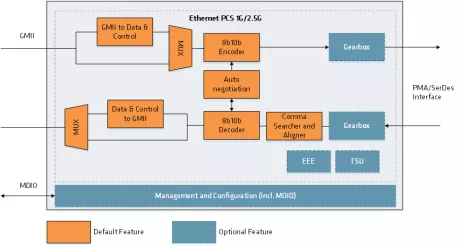

Ethernet PCS 1G/2.5G

- The Ethernet PCS 1G2.5G IP core is a silicon agnostic implementation of the Physical Coding Sublayer (PCS) compliant with Ethernet standard IEEE 802.3-2018.

- The IP core supports 1G and 2.5G line rates, however other Ethernet PCS speeds are available, such as 10G/25G and 100G.

- The IP provides an interface between the Media Access Control (MAC) and Physical Medium Attachment (PMA) through a Gigabit Media Independent Interface (GMII) or Serial Gigabit Media Independent Interface (SGMII).