Ethernet FEC Decoder IP

Filter

Compare

5

IP

from

4

vendors

(1

-

5)

-

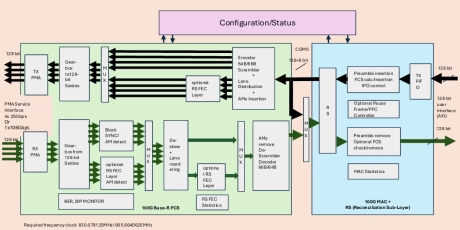

100G MAC/PCS Ultra Ethernet

- The IP integrates MAC Layer, RS Sub-Layer and 100G PCS Base-R cores according to IEEE 802.3 standard to provide seamless connection between an application and serdes interfaces

- 128-bit interface for TX and RX between MAC and the application Serdes interface – configurable to support PAM2 and PAM 4

-

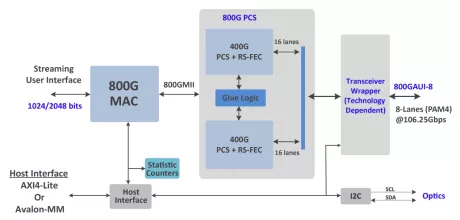

800 Gigabit Ethernet MAC + PCS

- Two 400GBase-R PCS cores with required modifications and glue logic.

- Includes RS-FEC(544,514) KP4 FEC

-

100G Reed-Solomon Codec for Ethernet IEEE 802.3 Clause 91 (803.3bj)

- FEC Sublayer for 100GBASE-CR4 and 100GBASE-KR4 PHY (clause 91 of the IEEE 802.3bj standard).

- 100G Ethernet MAC-friendly interface

-

10G/5G Verification IP

- Provides 10G/5G as per IEEE Std 802.3

- Supports Ethernet XGMII

- Supports XSBI

- Supports LX4 & CX4

- Supports LRM, CR, ER, LR

- Supports full duplex ethernet MAC

- Supports 64/66B PCS, BASE-R

- Supports 8B/10B PCS, BASE-X

- Supports FEC Decoder

- Supports PMD Training

- Supports AN

- Supports Ethernet XGMII

- Supports XSBI

- Supports LX4 & CX4

- Provides 10G/5G as per IEEE Std 802.3

-

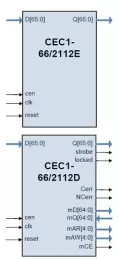

66/2112 Codec for Cyclic Code (2112,2080)

- Small Size

- Implements FEC Sublayer for 10GBASE-R (section 74 of the IEEE 802.3 standard)

- 10G/40G/100G Ethernet MAC-friendly interface

- Practically self-contained: requires only memory for one 2112-bit block in the decoder.