Elliptic Curve Crypto Accelerator IP

Filter

Compare

8

IP

from

5

vendors

(1

-

8)

-

Crypto Box Toolset Secure Accelerator

- The High-Performance Hybrid Crypto Box IP core delivers maximum cryptographic throughput by combining classical asymmetric (RSA, ECC), symmetric (AES), and hashing (SHA-2/HMAC) engines with a dedicated post-quantum accelerator supporting ML-KEM (Kyber) and ML-DSA (Dilithium).

- Designed for performance-critical systems without tight area or power limitations, this IP enables ultra-fast key exchange, digital signatures, and secure data processing.

-

Crypto Box Toolset Secure Accelerator

- The Hybrid Crypto Box IP core is a comprehensive, high-efficiency cryptographic solution that combines RSA, ECC, AES, and SHA-2/HMAC with a built-in accelerator for post-quantum algorithms such as ML-KEM (Kyber) and ML-DSA (Dilithium). Designed for embedded systems with balanced resource constraints, it enables secure key exchange, digital signatures, authenticated encryption, and hashing, future-proofed for the quantum era.

-

Crypto Box Toolset Secure Accelerator

- The Crypto Box IP core is a high-efficiency cryptographic solution that combines RSA, ECC, AES, and a SHA-2/HMAC engine, all with advanced protections against side-channel and fault injection attacks.

- Designed for devices with balanced budgets for performance, area, and power, it enables secure key exchange, digital signatures, data encryption, and message authentication in a unified, compact architecture.

-

Crypto Box Toolset Secure Accelerator

- The Crypto Box IP core is a compact, power-efficient cryptographic engine that combines essential asymmetric algorithms (RSA, ECC) with high-speed AES encryption in a single integrated block.

- Designed for resource-constrained embedded systems, it enables secure key exchange, digital signatures, and fast data encryption with minimal area and power overhead.The

-

Agile Post Quantum Crypto (PQC) Public Key Accelerator - NIST algorithms

- Offloads the computationally intensive parts of public key cryptography

- Support for ARM® AMBA® AHB™/AXI™ and synchronous RAM interfaces

- Integer operations (512-, 768-, 1024-, 1536-, 2048-, 3072-, and 4096-bit)

- ECC-GF(p) operations (160, 192, 224, 256, 384, 512 and 521-bit)

-

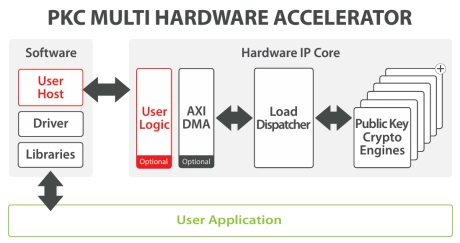

PKC Multi Hardware Accelerator IP

- The PKC Multi hardware accelerator is a secure connection engine that can be used to offload the compute intensive Public Key operations (Diffie-Hellman Key Exchange, Signature Generation and Verification), widely used for High-performance TLS Handshake.

-

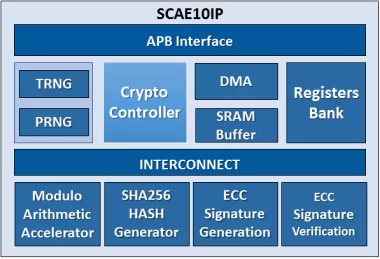

Cryptographic Cores IP

- The Cryptographic Cores IP portfolio delivers secure, high-performance implementations of symmetric, asymmetric, and post-quantum algorithms.

- Designed for low-area, low-latency operation, the silicon-proven cores help SoC designers and embedded teams build trusted, efficient devices for IoT, automotive, medical, and industrial markets.

-

USB Type-C Authentication IP

- Fully compliant with USB PD Specification revision 3.0 and Type-C Cable and Connector specification revision 1.2