ESD IP

Filter

Compare

858

IP

from

48

vendors

(1

-

10)

-

Stand-Alone ESD Cell in GF 28nm

- This ESD library is a silicon-proven set of discrete, pad-independent ESD clamps for GlobalFoundries 28nm technology.

- The library is designed to provide robust ESD protection for power domains and low-speed signals in advanced SoCs where traditional pad-based protection is insufficient or impractical.

-

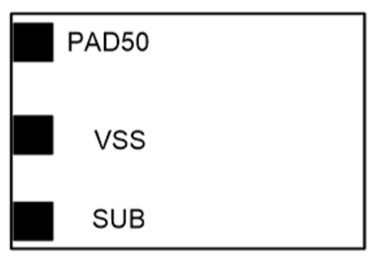

Analog I/O Library with a custom 12V ESD Solution IN GF 55nm

- This I/O library is a silicon-proven, flip-chip-optimized analog and mixed-signal I/O Library for GlobalFoundries 55nm BCD technology.

- It provides a comprehensive set of 1.8V, 3.3V, 5V, and 12V analog I/O and power pads, designed for robust ESD protection, flexible pad-ring construction, and reliable operation across industrial temperature ranges.

-

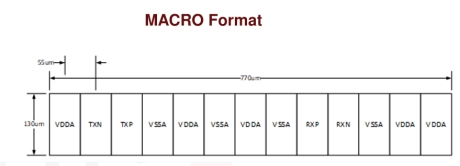

ESD Solutions for Multi-Gigabit SerDes in TSMC 28nm

- A Wirebond and FlipChip compatible <80fF ESD Solutions for Multi-Gigabit SerDes Applications.

- This silicon-proven TSMC 28nm Digital I/O Library delivers a low-capacitance, high-reliability interface solution optimized for advanced semiconductor applications.

- Featuring low-capacitance LVDS differential pairs (<250fF per pin) at 0.8V, this library ensures superior signal integrity for high-speed applications.

-

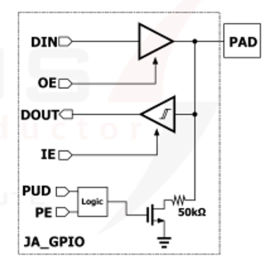

High-Speed 3.3V I/O library with 8kV ESD Protection in TSPCo 65nm

- A 3.3V wirebond I/O library with 8kV HBM ESD protection, a 1.2Gbps LVDS, GPIO, and I2C compliant ODIO in an ultra-small footprint.

- This library ensures robust reliability in challenging environments, with capabilities including 8kV HBM, 500V CDM, and a robust 2kV IEC 61000-4-2 system stress capability.

- Its compact footprint makes it ideal for applications where size is critical.

-

Full Radiation-Hardened ESD Library in GF 12nm LP/LP+

- Full ESD Library for Powers and I/O

- I/O Protection

- Full Library is Latch-up proven to 200mA at -40C to 125C

- Radiation Hardened 64 MeV proton test and >1.3E+09 flux

-

ESD Cells

- ESD structure for High-Speed analog input/output, and supply clamps

- GlobalFoundries - 45SPCLO

-

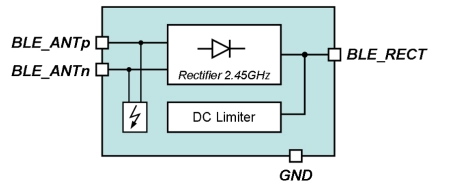

0.8 to 2.5GHz full wave rectifier with ESD protection

- GF 130nm Embedded EEPROM technology process

- Input voltage limit with up to 20mA shunt capability

-

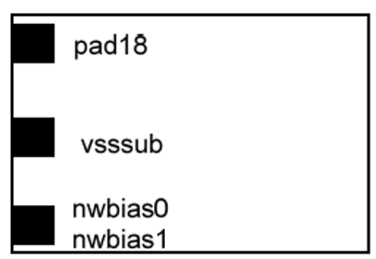

RF ESD library in TSMC 55nm LP

- RF ESD cells in TSMC 55nm LP targetting low-capacitance ESD protection.

- This library is a production-quality, silicon-proven ESD library in TSMC 55nm.

- The library does not have general ESD architecture as it is not a full I/O, but rather is a collection of standalone ESD cells that target low-capacitance RF ESD protection.

-

6.5V ESD Clamp in 180nm Technology

- 1.8V/5V FETs

- 1P6M with 2fF MiMs

- Temperature: -40C to 125C

- Metallization for cell is M1-M5

-

5V ESD Clamp in GlobalFoundries 180nm LPe

- A GlobalFoundries 180nm LPe Specialized 5V ESD Clamp.

- A key attribute of this 5V Clamp is that it can be used for either signal protection or 1.8V power supplies.

- The clamp is a single cell, 44um x 32um in size. It is built from the substrate to metal 6.