DisplayPort v1.4 IP

Filter

Compare

24

IP

from

6

vendors

(1

-

10)

-

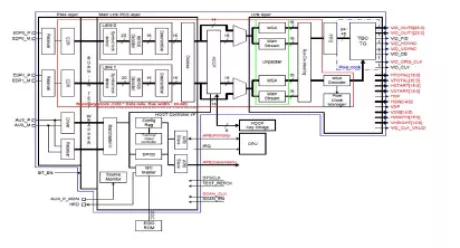

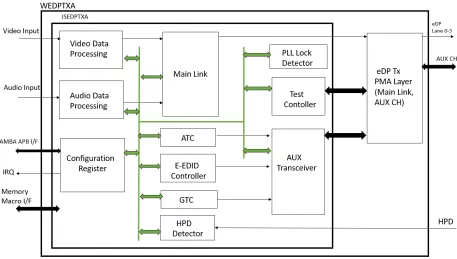

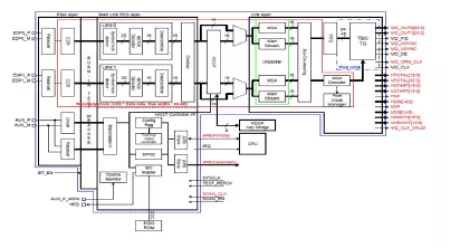

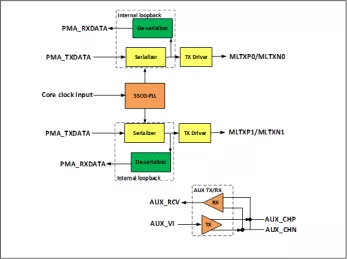

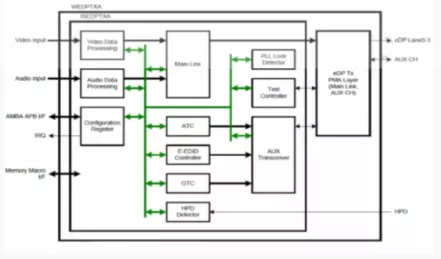

Display Port v1.4 Tx PHY & Controller IP, Silicon Proven in TSMC 12FFC

- eDP version 1.4a / DP version 1.4 compliant transmitter

- Supports HDCP1.4 and HDCP2.2(Optional)

- Supports Forward Error Correction (Optional)

- Consists of configurable (4/2/1) link channels and one AUX channel

-

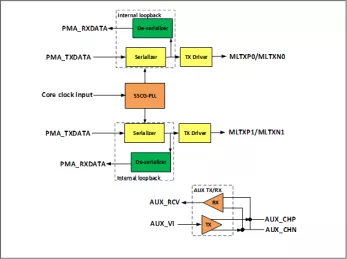

Display Port v1.4 Rx PHY & Controller IP, Silicon Proven in TSMC 40LP

- DisplayPort version 1.4 compliant receiver

- PHY supports 1.62Gbps (RBR) to 5.4Gbps (HBR2) bit rate

- Integrated 100-ohm termination resistors with common-mode biasing

- Integrated equalizer with tunable strength

-

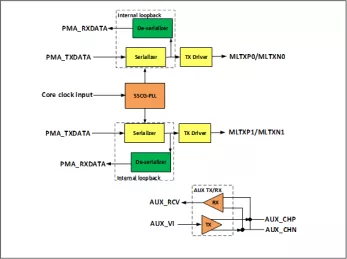

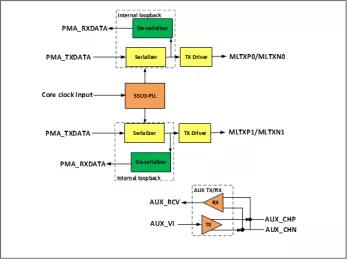

DisplayPort TX v1.4, 8.1Gbps x2-lane, TSMC 28HPC+, N/S orientation

- Supports 1.62G to 20Gbps data rates and compact die area

- Supports x1, x2 and x4 lanes

- Supports post-cursor 1 FFE for Main Link transmitter

- Supports four swing levels for Main Link transmitter

-

DisplayPort TX v1.4, 8.1Gbps x2-lane, TSMC 12FFC, N/S orientation

- Supports 1.62G to 20Gbps data rates and compact die area

- Supports x1, x2 and x4 lanes

- Supports post-cursor 1 FFE for Main Link transmitter

- Supports four swing levels for Main Link transmitter

-

DisplayPort TX v1.4, 8.1Gbps x2-lane, TSMC N7, 1.8V, N/S orientation

- Supports 1.62G to 20Gbps data rates and compact die area

- Supports x1, x2 and x4 lanes

- Supports post-cursor 1 FFE for Main Link transmitter

- Supports four swing levels for Main Link transmitter

-

DisplayPort TX v1.4, 8.1Gbps x2-lane, TSMC N6, 1.8V, N/S orientation

- Supports 1.62G to 20Gbps data rates and compact die area

- Supports x1, x2 and x4 lanes

- Supports post-cursor 1 FFE for Main Link transmitter

- Supports four swing levels for Main Link transmitter

-

Display Port v1.4 Rx PHY & Controller IP, Silicon Proven in UMC 55SP

- DisplayPort version 1.4 compliant receiver

- PHY supports 1.62Gbps (RBR) to 5.4Gbps (HBR2) bit rate

- Integrated 100-ohm termination resistors with common-mode biasing

- Integrated equalizer with tunable strength

-

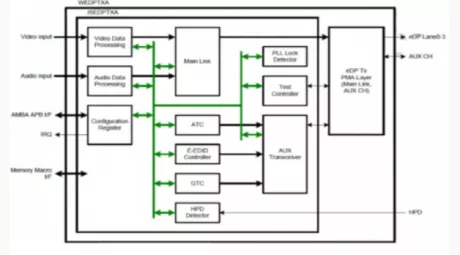

Display Port v1.4 Tx PHY & Controller IP, Silicon Proven in UMC 55SP

- eDP version 1.4a / DP version 1.4 compliant transmitter

- Supports HDCP1.4 and HDCP2.2(Optional)

- Supports Forward Error Correction (Optional)

- Consists of configurable (4/2/1) link channels and one AUX channel

-

Display Port v1.4 Tx PHY & Controller IP, Silicon Proven in TSMC 40LP

- eDP version 1.4a / DP version 1.4 compliant transmitter

- Supports HDCP1.4 and HDCP2.2(Optional)

- Supports Forward Error Correction (Optional)

- Consists of configurable (4/2/1) link channels and one AUX channe

-

Display Port v1.4 Rx PHY & Controller IP, Silicon Proven in UMC 40SP

- DisplayPort version 1.4 compliant receiver

- PHY supports 1.62Gbps (RBR) to 5.4Gbps (HBR2) bit rate

- Integrated 100-ohm termination resistors with common-mode biasing

- Integrated equalizer with tunable strength