Display Processor IP

Filter

Compare

265

IP

from

24

vendors

(1

-

10)

-

High-quality and powerful display processor

- Support 8K@60FPS or multiple 4K@120FPS

- All common HDR formats, including HDR10, HDR10+ and HLG

- Security Features for Content Protections

- Subjective and objective image quality

-

Display Processor for VR

- Superior User Experiences on Mobile

- Efficiency and Bandwidth Savings

- Increased Performance, Same Footprint

-

Scalable and flexible display processor

- Leading Performance per Area

- Extreme Low Power Design

- Display Output

- AXI bus Interfaces

-

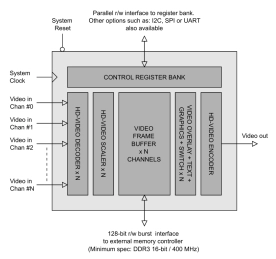

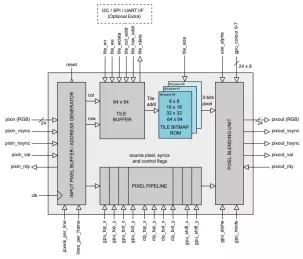

HD Multi-window Video Processor IP Core

- This brief specification describes the operation of the HD Multi-window Video Processor (evaluation) IP Core.

- The IP Core is provided as a netlist in either EDIF, Verilog or VHDL formats.

-

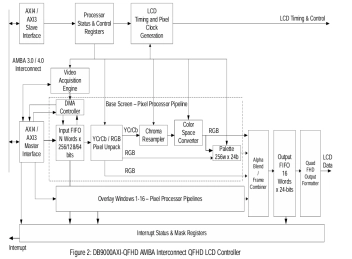

Display Controller – Ultra HD LCD / OLED Panels (AXI4/AXI Bus)

- The DB9000AXI4-UHD LCD Controller IP Core interfaces a video image in frame buffer memory via the AMBA 3.0 / 4.0 AXI Protocol Interconnect to an 4K/8K TFT LCD / OLED display panel.

- The video image in frame buffer memory can be 8/10/12-bit 4:2:0 or 4:2:2 or 4:4:4 sampled YCrCb video or 4:4:4 RGB. For 4:2:0 and 4:2:2 YCrCb, the chroma components are re-sampled to 4:4:4 and color converted to RGB.

-

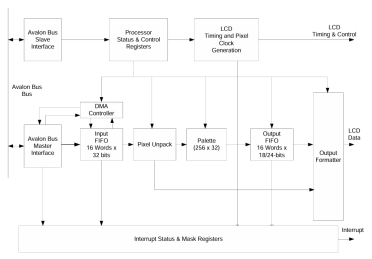

Display Controller – LCD / OLED Panels (Avalon Bus)

- The DB9000AVLN TFT LCD Controller IP Core interfaces a microprocessor and frame buffer memory via the Avalon Bus within Altera Qsys Integration (generating the System Interconnect Fabric) to a TFT LCD panel.

- In an Altera FPGA, typically, the microprocessor is a NIOS II or ARM processor and frame buffer memory is either on-chip SRAM memory or larger off-chip SRAM or SDRAM.

-

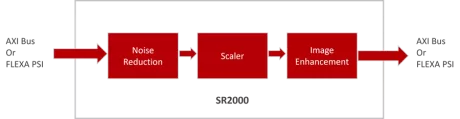

Pixel processor - High Image Quality Super Resolution

- Enables transfer of low-resolution sources to reduce bandwidth, while allowing high quality and high resolution to be displayed at the edge

- Offers robust pixel processing features and can perform detail enhancement without changing the color and saturation.

-

Graphics Processor Overlay IP Core

- Technology independent soft IP Core for FPGA, ASIC and SoC devices

- Supplied as human-readable VHDL (or Verilog) source code

-

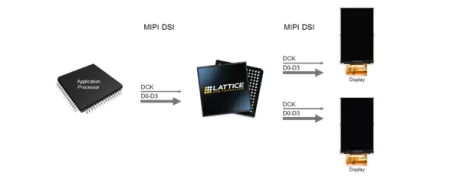

One Input to Two Output MIPI DSI Display Splitter Bridge

- Supports MIPI DSI up to 6 Gbps per MIPI D-PHY

- Provides one or two MIPI DSI outputs

- Supports all MIPI DSI data types

- Provides a DCS (Display Command Set) controller to program the display, ROM data used only for DSI in HS or LPDT mode – ROM is programmable by user

-

One Input to One Output MIPI DSI Display Interface Bridge

- Supports MIPI DSI up to 6 Gbps per MIPI D-PHY

- Provides one or two MIPI DSI outputs

- Supports all MIPI DSI data types

- Provides a DCS (Display Command Set) controller to program the display, ROM data used only for DSI in HS or LPDT mode – ROM is programmable by user