Display Controller IP

Filter

Compare

393

IP

from

37

vendors

(1

-

10)

-

LCD Display controller

- 24-bit RGB or 20-bit BT1120 parallel pixel output; 8 bits-per-pixel (RGB888)

- 1 display FIFO (32x24-bit)

- Color look-up table (CLUT) up to 256 color (256x24-bit) per layer

- Programmable timings for different display panels (Refer to :ref:Synchronou_timing)

-

Display Controller – Ultra HD LCD / OLED Panels (AXI4/AXI Bus)

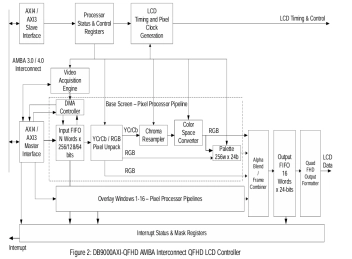

- The DB9000AXI4-UHD LCD Controller IP Core interfaces a video image in frame buffer memory via the AMBA 3.0 / 4.0 AXI Protocol Interconnect to an 4K/8K TFT LCD / OLED display panel.

- The video image in frame buffer memory can be 8/10/12-bit 4:2:0 or 4:2:2 or 4:4:4 sampled YCrCb video or 4:4:4 RGB. For 4:2:0 and 4:2:2 YCrCb, the chroma components are re-sampled to 4:4:4 and color converted to RGB.

-

Display Controller – LCD / OLED Panels (Avalon Bus)

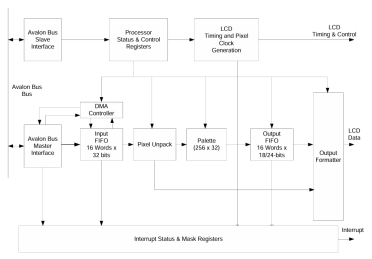

- The DB9000AVLN TFT LCD Controller IP Core interfaces a microprocessor and frame buffer memory via the Avalon Bus within Altera Qsys Integration (generating the System Interconnect Fabric) to a TFT LCD panel.

- In an Altera FPGA, typically, the microprocessor is a NIOS II or ARM processor and frame buffer memory is either on-chip SRAM memory or larger off-chip SRAM or SDRAM.

-

Display Controller IP

- Target Display Resolution: 4KX2K

- MIPI-DPI Interfaces Support

- HDMI/DP/eDP Interfaces Support

- Default Layers:5

-

Display Controller IP

- Target Display Resolution: 4KX2K

- MIPI-DPI Interfaces Support

- HDMI/DP/eDP Interfaces Support

- Default Layers:6

-

Display Controller IP

- Target Display Resolution: 1080P

- MIPI-DBI Interfaces Support

- MIPI-DPI Interfaces Support

- Default Layers:1

-

Display controller for dual-display

- Scan directions: 90/180/270° rotation, horizontal/vertical flip

- Multiple layers (alpha blend) with configurable mapping

-

Customizable Display Controller IP

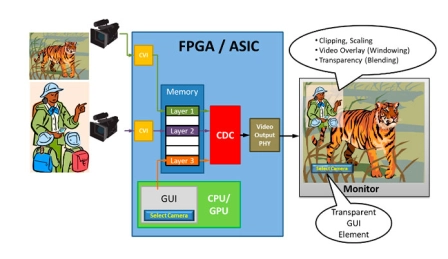

- CDC is a fully Customizable Display Controller IP supporting up to 16k resolutions (4096x4096 pixel) on a MIPI-DPI compliant parallel video output.

- Several features can be configured at synthesis time and programmed at run time.

- The display controller can be applied to e.g. FPGA systems with a resource optimized, application specific feature configuration or to ASIC projects applying a more generic feature set and thus more flexibility.

-

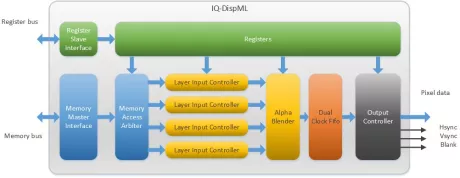

Multilayer Configurable Display Controller

- Fully programmable clock and timing control for flat panel displays with progressive scanning

- Support for resolutions up to 4096x4096

- Completely variable timing parameters, for standard or specific display resolutions

- Support for 8,16, 18 or 24 bit RGB output color depth

-

Display Controller

- Support for parallel, LVDS, HDMI/DVI and CameraLink displays without external display controller device

- Support for unlimited video pages

- Built-in PWM generator for display brightness control

- Optional 2D accelerator unit (draw/copy rectangles, supports transparent color)