DDR5 DRAM IP

Filter

Compare

63

IP

from

10

vendors

(1

-

10)

-

DDR5 & DDR4 COMBO IO for memory controller PHY, 4800Mbps on TSMC 12nm

- The DDR5&DDR4 COMBO IO is used to transfer the Command/Address/Clk and Data between the memory controller PHY and the DRAM device

- The TX is designed to send information from PHY to DRAM and RX is designed to receive information which is from DRAM._x000D_ It supports DDR5&DDR4 interface

- The DDR5 DQ data rate can be up to 4800Mb/s, and the DDR4 DQ data rate can be up to 3200Mb/s and CA is SDR mode.

-

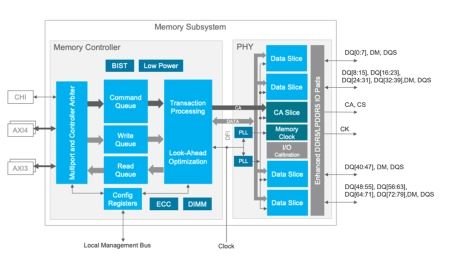

DDR5 MRDIMM PHY and Controller

- The DDR5 12.8Gbps MRDIMM Gen2 PHY and controller memory IP system solutions double the performance of DDR5 DRAM.

- The DDDR5 12.8Gbps design and architecture address the need for greater memory bandwidth to accommodate unprecedented AI processing demands in enterprise and data center applications, including AI in the cloud.

-

Simulation VIP for DDR5 DIMM

- DIMM Types

- DDR5 UDIMM, RDIMM, and LRDIMM

- Size

- 32Gb, 64Gb, and 128Gb

-

Simulation VIP for DDR5

- Speeds

- 3200, 3600, 4000, 4400, 4800, 5200, 5600, 6000, and 6400

- Density

- 8Gb, 16Gb, 24Gb, 32Gb, and 64Gb

-

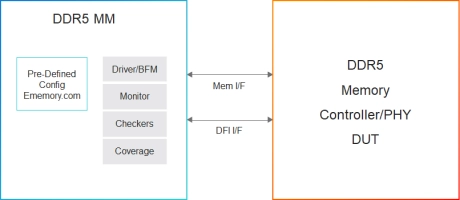

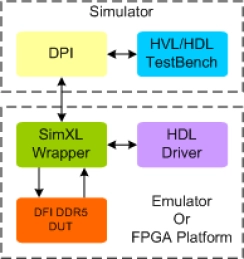

DDR5 DFI Synthesizable Transactor

- Compliant with DFI 5.0 Specification.

- DFI-DDR5 Applies to :

- DDR5 protocol standard JESD79-5 & JESD79-5 Rev1.40 (Draft) Specifications

- Supports all Interface Groups.

-

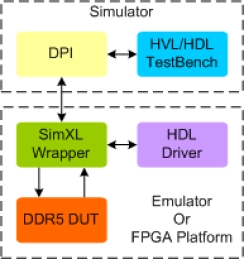

DDR5 Synthesizable Transactor

- Supports 100% of DDR5 protocol standard JESD79-5 & JESD79-5 Rev1.40 (Draft)

- Supports all the DDR5 commands as per the specs

- Supports up to 64GB device density

- Supports the following devices:

-

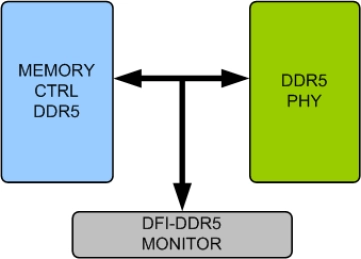

DDR5 DFI Verification IP

- Compliant with DFI 5.0 Specification.

- DFI-DDR5 Applies to :

- DDR5 protocol standard JESD79-5 & JESD79-5 Rev1.40 (Draft) Specifications

- Supports all Interface Groups.

-

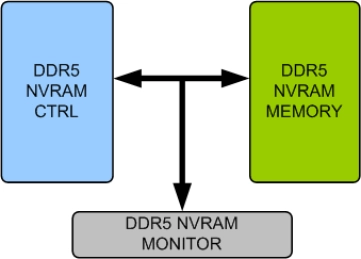

DDR5 NVRAM Memory Model

- Supports DDR5 NVRAM memory devices from all leading vendors.

- Supports 100% of DDR5 NVRAM protocol standard JESD79-5 (Draft).

- Supports all the DDR5 NVRAM commands as per the specs.

- Supports up to 1 TB device density.

-

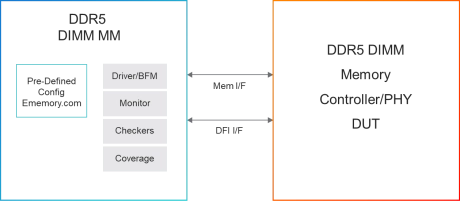

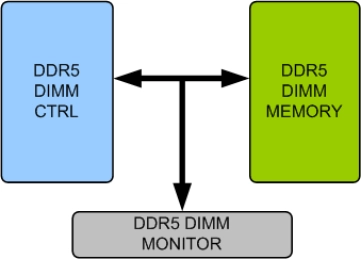

DDR5 DIMM Memory Model

- Supports DDR5 DIMM memory devices from all leading vendors.

- Supports 100% of DDR5 DIMM protocol standard.

- Supports DDR5 RDIMM and LRDIMM types.

- Supports all the DDR5 DRAM features.

-

DDR5 Memory Model

- Supports DDR5 memory devices from all leading vendors.

- Supports 100% of DDR5 protocol standard JESD79-5 & JESD79-5 Rev1.40 (Draft).

- Supports all the DDR5 commands as per the specs.

- Supports up to 64GB device density.