ARM Cortex M0 IP

Filter

Compare

6

IP

from

4

vendors

(1

-

6)

-

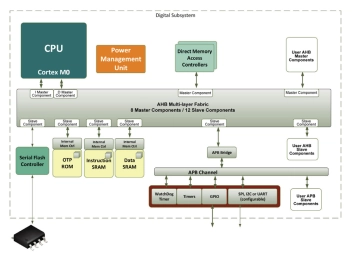

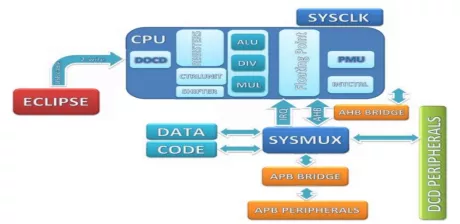

AHB Performance Subsystem - ARM Cortex M0

- The AHB Performance Subsystem is an AMBA® based system that is useful as the digital infrastructure for building low power SOCs needing additional performance.

- This AHB Multi-matrix system contains a flexible Power Management Unit for controlling power sequencing of the CPU and peripherals.

- The PMU can easily be extended to control additional cores, peripherals and even analog subsystems on the same SOC

-

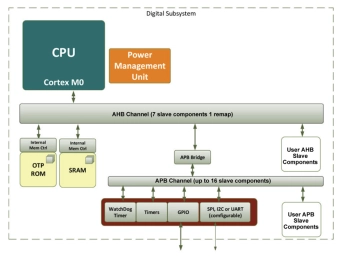

AHB Low Power Subsystem - ARM Cortex M0

- The AHB Low Power Subsystem is an AMBA® based system that is useful as the basic digital infrastructure for building low power SOCs.

- The subsystem contains a flexible Power Management Unit that controls the power sequence of the CPU as well as the APB peripherals.

- The PMU can easily be extended to control additional cores, peripherals and even mixed signal subsystems on the same SOC.

-

-

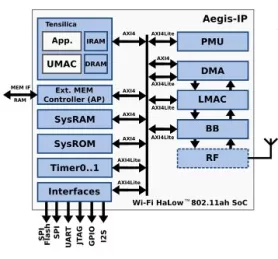

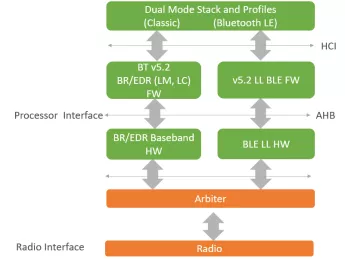

Bluetooth Dual Mode v5.3 Baseband Controller IP

- Software Memory footprint (ARM Cortex M0/M3): ROM ~ 300KB ; RAM ~ 112 KB

- Combined Hardware gate count : 250 k gates

- Arbitration logic implemented in hardware and assisted by software

- Baseband and LE LL Accelerator

-

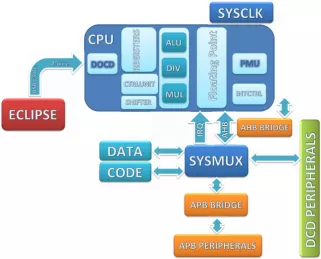

D32Pro IP

- ASIC Silicon proven architecture

- Performance up to 1.48 / 2.67 DMIPS/MHz and 2.41 CoreMarks/MHz

- Small footprint starting at 10.6k / 6.7k ASIC gates

- Dynamic power below 7 uW/MHz in 90nm

-

Scalable & Royalty-Free 32-bit CPU

- Configurable 32-bit Harvard architecture

- Performance up to 1.48 / 2.67 DMIPS/MHz and 2.41 CoreMarks/MHz

- Small footprint starting at 10.6k/6.8k ASIC gates