ARM Cortex IP

Filter

Compare

65

IP

from

18

vendors

(1

-

10)

-

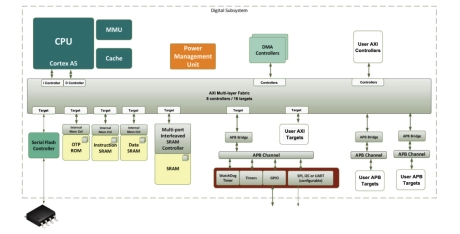

AXI Performance Subsystem - ARM Cortex A

- The AXI Performance Subsystem is an AMBA® AXI4 based system that is useful as the digital infrastructure for building SOCs needing high performance.

- This system contains an 8 Master component, 16 Slave component AXI4 multi-matrix for supporting multiple high speed user AXI Master components while providing high performance with Cortex-A5 class processors.

-

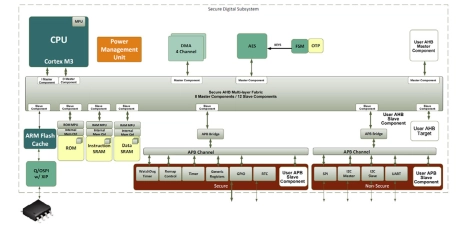

AHB Secure Subsystem - ARM Cortex M3

- The Secure AHB Performance Subsystem is a high-performance AHB subsystem that allows for a high level of hardware and software security.

- It integrates a security-conscious processor, the ARM Cortex-M3, with a security-conscious low power high-performance subsystem.

- Everything is pre-integrated with the necessary AHB and APB IP cores needed to run a small software kernel or a Real Time Operating System (RTOS).

-

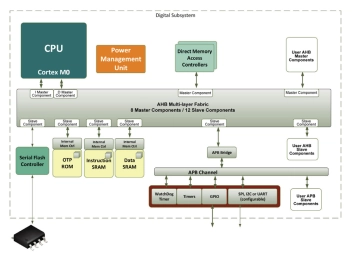

AHB Performance Subsystem - ARM Cortex M0

- The AHB Performance Subsystem is an AMBA® based system that is useful as the digital infrastructure for building low power SOCs needing additional performance.

- This AHB Multi-matrix system contains a flexible Power Management Unit for controlling power sequencing of the CPU and peripherals.

- The PMU can easily be extended to control additional cores, peripherals and even analog subsystems on the same SOC

-

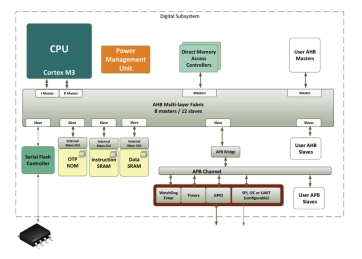

AHB Performance Subsystem - ARM Cortex M3

- The AHB Performance Subsystem is an AMBA® based system that is useful as the digital infrastructure for building low power SOCs needing additional performance.

- This AHB Multi-matrix system contains a flexible Power Management Unit for controlling power sequencing of the CPU and peripherals.

- The PMU can easily be extended to control additional cores, peripherals and even analog subsystems on the same SOC.

-

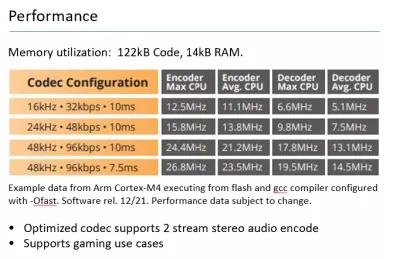

LC3 / LC3plus Bluetooth LE Audio Codecs for Arm Cortex M4 & M33

- Bluetooth SIG Qualified

- Production proven IP, extensively tested, commercially shipping

- High-Quality Audio with LC3 Codec

- • 7.5ms and 10ms frame lengths

-

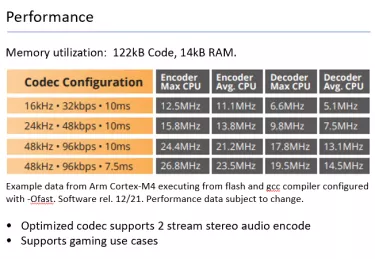

LC3 / LC3plus Bluetooth LE Audio Codecs for Arm Cortex M55

- Bluetooth SIG Qualified

- Production proven IP, extensively tested, commercially shipping

- High-Quality Audio with LC3 Codec

-

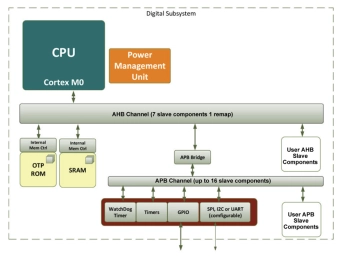

AHB Low Power Subsystem - ARM Cortex M0

- The AHB Low Power Subsystem is an AMBA® based system that is useful as the basic digital infrastructure for building low power SOCs.

- The subsystem contains a flexible Power Management Unit that controls the power sequence of the CPU as well as the APB peripherals.

- The PMU can easily be extended to control additional cores, peripherals and even mixed signal subsystems on the same SOC.

-

Arm Cortex-M52 Processor

- Smallest Area, Energy-Efficient Processor for AIoT

- Simplify Software Development

- Faster Route to Security Certification

-

Highest Performance CPU with Split-Lock

- Highest Sustained Performance

- Scalable, Heterogeneous Compute

- Flexibility with Split-Lock