AES-32 Cryptographic Accelerator IP

Filter

Compare

8

IP

from

5

vendors

(1

-

8)

-

AES Core G2

- Fully synchronous with single clock and enable

- Configurable via VHDL generic parameters to trade features and performance against area

- Source code available for security review

- Cost Effective Royalty Free licencing with a variety of options to suit project requirements

-

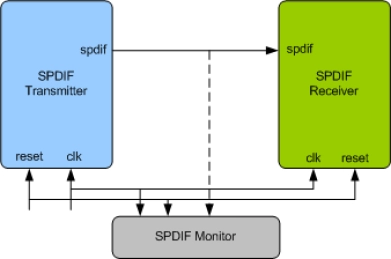

SPDIF (IEC60958) Verification IP

- Full SPDIF functionality as per specs IEC 60958 and IEC 61937.

- Supports SMPTE 337M standards for non Linear PCM Audio

- Supports AES/EBU, AES3 standards for Linear PCM Audio

- Supports following sampling/Driving rates,

-

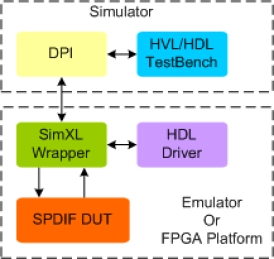

SPDIF Synthesizable Transactor

- Supports full SPDIF functionality as per specs IEC 60958 and IEC 61937

- Supports SMPTE 337M standards for non Linear PCM Audio

- Supports AES/EBU, AES3 standards for Linear PCM Audio

- Supports following sampling/driving rates,

-

IPMX Encoder and Decoder

- TR-08 Compliant (requires JPEG-XS Core)

- Included IPMX support

- Fully integrated and modular solution

-

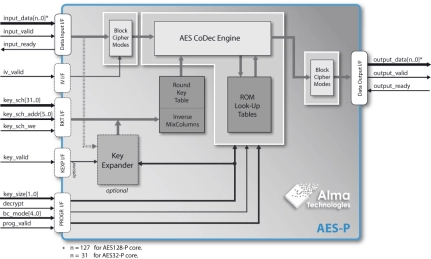

AES Encryption & Decryption IP Core − Programmable Block Cipher Modes

- The AES-P IP core implements the FIPS-197 Advanced Encryption Standard. It can be programmed to encrypt or decrypt 128-bit blocks of data, using 128-, 192-, or 256-bit cipher-key.

- The Block Cipher mode of operation is run-time programmable to ECB, CBC, CFB, OFB, or CTR. The AES-P core is available in two variations, the standard AES32-P and the fast AES128-P.

-

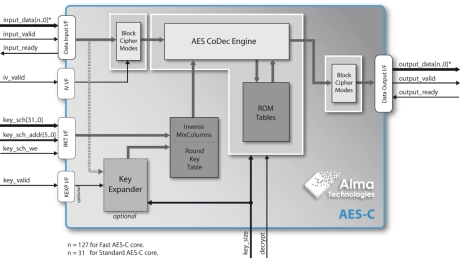

AES Encryption & Decryption IP Core − Single Configurable Block Cipher Mode

- Compliant, High-Performance and Standalone Operation

- Trouble-Free Technology Map and Implementation

-

Configurable SPDIF-AES3 Transmitter

- The SPDIF-Tx-Pro (CWda15) is a digital audio transmitter IP core supporting the SPDIF IEC60958 and AES3 standards for PCM audio and the IEC61937 and SMPTE 337M standards for non-PCM (compressed) audio.

- The core is very configurable allowing many features of the standards to be optionally supported by hardware or software.

-

Configurable SPDIF-AES3 Receiver

- The SPDIF-Rx-Pro (CWda14) is a digital audio receiver IP core supporting the SPDIF and AES3 and IEC60958 standards and also adds hardware support for the IEC61937 and SMPTE 337M standards for non-PCM (compressed) audio.

- This purely digital clock and data recovery method dispenses the classical analog PLL at the input reducing the receiver cost.