5G LDPC Encoder IP

Filter

Compare

11

IP

from

7

vendors

(1

-

10)

-

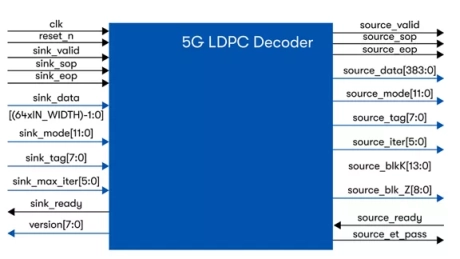

5G LDPC Encoder / Decoder

- CRC encoding

- Filler bits insertion/removal

- LDPC encoding (basegraph1 and 2, all Z-values)

-

LDPC Encoder / Decoder for 5G and 6G NTN PHY

- AccelerComm LDPC provides licensable, 3GPP-compliant encoder and decoder IP cores optimised for terrestrial, transparent NTN, and regenerative satellite PHY architectures.

- Its high-throughput, low-latency design is FPGA- and ASIC-ready, with area-efficient implementations suited to SWaP-constrained satellite payloads and high-density ground infrastructure alike.

-

5G-NR LDPC Encoder

- High-throughput design.

- Low-power and low-complexity design.

- Block-to-block on-the-fly configuration.

- AXI4-Stream handshaking interfaces for seamless integration.

-

LDPC Encoder / Decoder

- Optimized for 5G Wireless (backhaul and baseband) and DOCSIS 3.1 applications

- Highly configurable codes

- Normalized min-sum decoding algorithm

-

LDPC for 5G DVBS2 802.11

- High throughput

- One encoder and decoder per matrix

- Five cycles per iteration may increase to around 10 for timing between gates.

- Has configuration parameters for stopping if code is diverging.

-

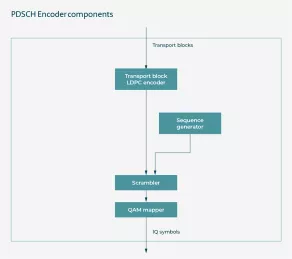

PDSCH Encoder for 3GPP 5G NR

- The PDSCH Encoder and PUSCH Decoder products simplify the creation of high performance 5G NR implementations.

- PDSCH Encoder features the new QAM mapper and Scrambler functionality. These are integrated with LDPC encoder chain and transport block chain components.

- PDSCH encoder has a configurable IQ parallelism for improved performance per clock.

- The functions included are CRC, Segmentation, LDPC encode, Rate matching, Integrated HARQ, Concatenation, Scrambling and Modulation.

-

Flexible LDPC encoder/decoder

- Flexible LDPC codes, hundreds of codes can be handled simultaneously, run-time reconfigurable

- Supports expansion factor ranging from 2 to 1024

-

LDPC Intel® FPGA IP

- Low-density parity-check (LDPC) codes are linear error correction codes that allow you to transmit messages over noisy channels.

- Intel's 5G Low-Density Parity Check (LDPC) Intel FPGA Intellectual Property (IP) core is a high-throughput encoder or decoder that is compliant with 3rd Generation Partnership Project (3GPP) 5G specification.

-

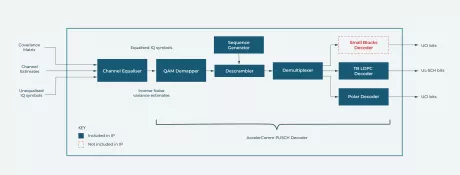

PUSCH Equalizer for 3GPP 5G NR

- Complete implementation of the relevant 3GPP standards

- Improved spectral efficiency across low SINR range against industry-standard simulation toolbox

-

ASIC IP-core for very-high-throughput decoding (>20G) of 3GPP 5G Release 15

- Portable to all ASIC and FPGA technologies