2.5D GPU IP

Filter

Compare

10

IP

from

3

vendors

(1

-

10)

-

2.5D GPU

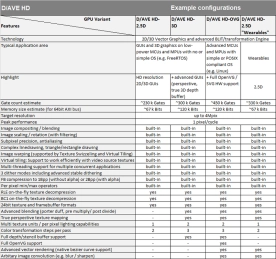

- The D/AVE HD 2.5D GPU family is an evolution of the D/AVE 2D family supporting high quality 2D and 3D rendering for displays up to 4K x 4K.

- Targeting modern graphics applications on high resolution displays in the Industrial, Medical, Military, Avionics, Automotive and Consumer markets, the D/AVE HD fixed-function 2.5D GPU core is designed to be fast with powerful functionality.

-

2.5D GPU IP Core - API Support: Vivante VGLite API, OpenVG 1.1

- Embedded Linux support

- Pixel Rate (Pixel/Cycle): 1

- Display Resolution: up to 4K

- API Support: Vivante VGLite API, OpenVG 1.1

-

2.5D GPU IP Core - API Support: Vector Graphics, VGLite API

- Embedded Linux support

- Pixel Rate (Pixel/Cycle): 1

- Display Resolution: up to 4K

- API Support: Vector Graphics, VGLite API

-

Vector Graphics IP

- Display Resolution: Up to 4K

- ROPS (Pixels Per Cycle) : 1

- API Support:Vector Graphics VGLite API

- Embedded Linux Support

-

TSMC N3P Source Sync 3DIO PHY

- Synopsys 3DIO IP Solution is a specialized IO for multi-die integration

- It includes multiple IP offerings for system-on-chip (SoC) designers to implement tunable, integrated multi-die design structures targeting HPC (AI), GPU, CPU, and mobile applications

- The optimal area of the 3DIO IP is carefully designed to be within the BUMP, providing significant advantages in implementation and signal routing

- Synopsys 3DIO IP Solution is architected to support 2.5D, 3D and SoIC package form factors, with flexible physical dimensions on u-BUMP or TSV integration

-

TSMC N3P Source Sync 3DIO Library

- Synopsys 3DIO IP Solution is a specialized IO for multi-die integration

- It includes multiple IP offerings for system-on-chip (SoC) designers to implement tunable, integrated multi-die design structures targeting HPC (AI), GPU, CPU, and mobile applications

- The optimal area of the 3DIO IP is carefully designed to be within the BUMP, providing significant advantages in implementation and signal routing

- Synopsys 3DIO IP Solution is architected to support 2.5D, 3D and SoIC package form factors, with flexible physical dimensions on u-BUMP or TSV integration

-

TSMC N3P 3DIO Library

- Synopsys 3DIO IP Solution is a specialized IO for multi-die integration

- It includes multiple IP offerings for system-on-chip (SoC) designers to implement tunable, integrated multi-die design structures targeting HPC (AI), GPU, CPU, and mobile applications

- The optimal area of the 3DIO IP is carefully designed to be within the BUMP, providing significant advantages in implementation and signal routing

- Synopsys 3DIO IP Solution is architected to support 2.5D, 3D and SoIC package form factors, with flexible physical dimensions on u-BUMP or TSV integration

-

TSMC N5 Source Sync 3DIO Library

- Synopsys 3DIO IP Solution is a specialized IO for multi-die integration

- It includes multiple IP offerings for system-on-chip (SoC) designers to implement tunable, integrated multi-die design structures targeting HPC (AI), GPU, CPU, and mobile applications

- The optimal area of the 3DIO IP is carefully designed to be within the BUMP, providing significant advantages in implementation and signal routing

- Synopsys 3DIO IP Solution is architected to support 2.5D, 3D and SoIC package form factors, with flexible physical dimensions on u-BUMP or TSV integration

-

TSMC N5 3DIO Library

- Synopsys 3DIO IP Solution is a specialized IO for multi-die integration

- It includes multiple IP offerings for system-on-chip (SoC) designers to implement tunable, integrated multi-die design structures targeting HPC (AI), GPU, CPU, and mobile applications

- The optimal area of the 3DIO IP is carefully designed to be within the BUMP, providing significant advantages in implementation and signal routing

- Synopsys 3DIO IP Solution is architected to support 2.5D, 3D and SoIC package form factors, with flexible physical dimensions on u-BUMP or TSV integration

-

TSMC N5 Source Sync 3DIO PHY

- Synopsys 3DIO IP Solution is a specialized IO for multi-die integration

- It includes multiple IP offerings for system-on-chip (SoC) designers to implement tunable, integrated multi-die design structures targeting HPC (AI), GPU, CPU, and mobile applications

- The optimal area of the 3DIO IP is carefully designed to be within the BUMP, providing significant advantages in implementation and signal routing

- Synopsys 3DIO IP Solution is architected to support 2.5D, 3D and SoIC package form factors, with flexible physical dimensions on u-BUMP or TSV integration