10G Ultra-low latency TCP/IP + MAC + PCS IP

Filter

Compare

1

IP

from

1

vendors

(1

-

1)

-

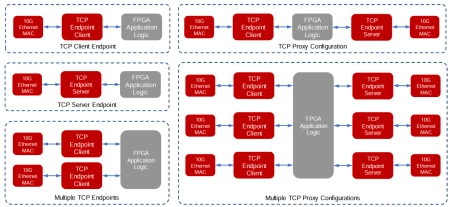

Ultra Low Latency 10G TCP Endpoint

- The TCP Endpoint implements a full, reliable streaming network stack in FPGA logic.

- It allows applications in logic to be directly connected to Internet Protocol (IP) interfaces by opening, maintaining, and closing TCP Connections via Ethernet to other hardware or software endpoints.