DDR6 IP

Welcome to the ultimate DDR6 IP hub! Explore our vast directory of DDR6 IP

All offers in

DDR6 IP

Filter

Compare

1

DDR6 IP

from

1

vendors

(1

-

1)

-

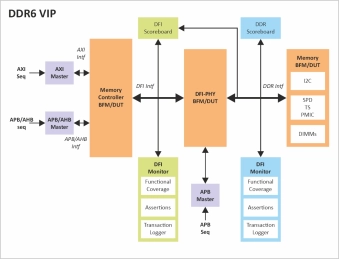

DDR6 Verification IP

- The DDR6 Verification IP provides an effective & efficient way to verify the components interfacing with DDR6 interface of an ASIC/FPGA or SoC.

- The DDR6 VIP is fully compliant with Standard DDR6 specification from JEDEC.

- This VIP is a light weight with an easy plug-and-play interface so that there is no hit on the design time and the simulation time.