Interface IP Cores for GLOBALFOUNDRIES

Welcome to the ultimate

Interface IP Cores

for

GLOBALFOUNDRIES

hub! Explore our vast directory of

Interface IP Cores

for

GLOBALFOUNDRIES

All offers in

Interface IP Cores

for

GLOBALFOUNDRIES

Filter

Compare

35

Interface IP Cores

for

GLOBALFOUNDRIES

from

4

vendors

(1

-

10)

Filter:

- 12nm

-

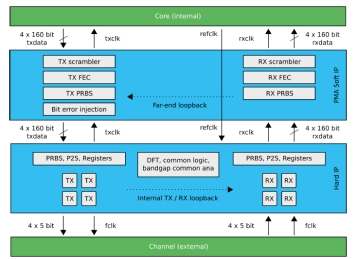

Ultra-short reach SerDes with 500 Gbit/s throughput

- 2x to 4x throughput at 50% or less energy consumption as compared to conventional SerDes over the same number of pins/wires

- High pin-efficiency and low power

- 208.3 Gbit/s full-duplex bandwidth per mm of die edge (500 Gbit/s for 2.4 mm of die edge)

-

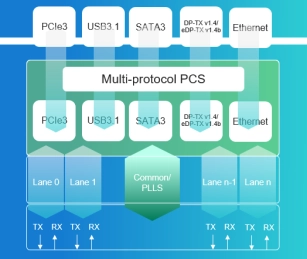

PHY for PCIe 3.1

- Supports PCIe 3.1, USB 3.1, DP-TX v1.4/eDP-TX v1.4b, SATA 3, 10G-KR and QSMII/SGMII

- Multi-protocol support for simultaneous independent links

- Supports SRIS and internal SSC generation

- Supports PCIe L1 sub-states

- Automatic calibration of on-chip termination resistors

- Supports internal and external clock sources with clock active detection

-

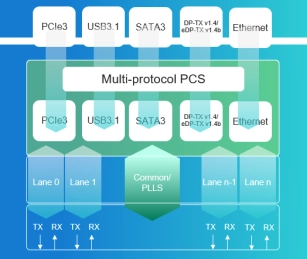

Ethernet SerDes - 16Gbps and 10Gbps multi-protocol SerDes PHY

- Wide range of protocols that support networking, HPC, and applications

- Low-latency, long-reach, and low-power modes

- Multi-Link PHY—mix protocols within the same macro

- EyeSurf —non-destructive on-chip oscilloscope

- Extensive set of isolation, test modes, and loop-backs including APB and JTAG

- Supports 16-bit, 20-bit, and 32-bit PIPE and non-PIPE interfaces

- Selectable serial pin polarity reversal for both transmit and receive paths

-

USB 2.0 femtoPHY - GF 12LPP18 x1, OTG, North/South (vertical) poly orientation

- Ported to over 50 different processes and configurations ranging from 65-nm to 14/16-nm FinFET

- Supports the USB 2.0 protocol and data rate (480 Mbps)

- Supports the USB Type-C specification

- USB femtoPHY, USB nanoPHY and USB picoPHY offer a tunability feature that allows quick, post-silicon adjustments that occur due to process variations, or unexpected chip and board parasitic, without modifying the existing design

-

USB 2.0 femtoPHY - GF 12LP x1, OTG, North/South (vertical) poly orientation

- Ported to over 50 different processes and configurations ranging from 65-nm to 14/16-nm FinFET

- Supports the USB 2.0 protocol and data rate (480 Mbps)

- Supports the USB Type-C specification

- USB femtoPHY, USB nanoPHY and USB picoPHY offer a tunability feature that allows quick, post-silicon adjustments that occur due to process variations, or unexpected chip and board parasitic, without modifying the existing design

-

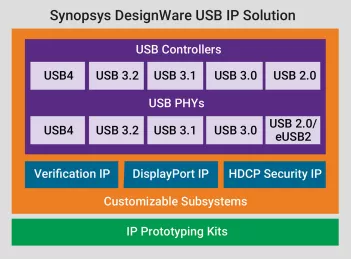

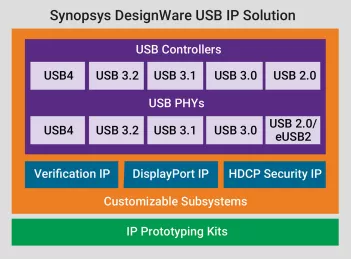

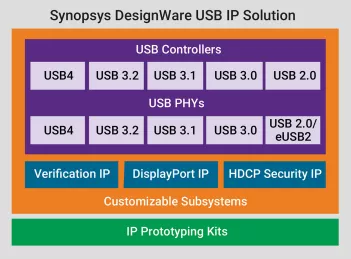

USB-C 3.2 DP/TX PHY for GF 12LP+, North/South poly orientation

- USB-IF certified Synopsys USB 3.2 solution

- VESA certified Synopsys DisplayPort 1.4 Tx solution

- Industry’s only USB Type-C IP solution consisting of USB-C 3.2/DisplayPort 1.4 TX PHYs, USB-C 3.2/DisplayPort 1.4 TX controllers with HDCP 2.2 and HDCP 2.2 content protection, verification IP, and IP subsystems

- Solution supports USB Type-C, SuperSpeed USB 3.2 at 20 Gbps, SuperSpeed USB 3.1 at 10 Gbps, SuperSpeed USB 3.0 at 5 Gbps and High-Speed USB (USB 2.0) as well as DisplayPort 1.4 TX supporting RBR, HBR1, HBR2 and HBR3 bitrates

-

PCIe 2.0 PHY, GF 12LP+ x2 North/South (vertical) poly orientation

- Compliant with the PCI Express (PCIe®) 2.1 and PIPE specifications

- x1, x2, x4, x8, x16 lane configurations with bifurcation

- PCIe L1 substate power management

- Supports power gating and power island

-

PCIe 2.0 PHY, GF 12LP+ x1, North/South (vertical) poly orientation

- Compliant with the PCI Express (PCIe®) 2.1 and PIPE specifications

- x1, x2, x4, x8, x16 lane configurations with bifurcation

- PCIe L1 substate power management

- Supports power gating and power island

-

PCIe 2.0 PHY, GF 12LP x2, North/South (vertical) poly orientation

- Compliant with the PCI Express (PCIe®) 2.1 and PIPE specifications

- x1, x2, x4, x8, x16 lane configurations with bifurcation

- PCIe L1 substate power management

- Supports power gating and power island

-

MIPI D-PHY Tx 4 Lanes - GF12LP18, North/South Poly Orientation

- Compliant with the MIPI D-PHY specification, v1.2

- Fully integrated hard macro

- Up to 2.5 Gbps per lane

- Aggregate throughput up to 10 Gbps in 4 data lanes