The PWM Verification IP provides an effective & efficient way to verify the PWM components of an IP or SoC. The VIP is fully compliant with IPWM Specification The VIP is light weight with easy plug-and-play components so that there is no hit on the design cycle time.

PWM Verification IP

Overview

Key Features

- Data registers of either 8,16,24 or 32-bit width.

- One global counter bus and four local counter buses are driven by Unified channels.

- Each channel has its own timebase, alternative to the counter buses.

- One global prescaler and one prescaler per channel.

- Timebases shared through the counter buses

- Control and status bits grouped in separated registers.

- Synchronization among timebases.

Benefits

- Available in native System Verilog (UVM/OVM/VMM) and Verilog

- Unique development methodology to ensure the highest levels of quality

- 24X5 customer support

- Unique and customizable licensing models

- Exhaustive set of assertions and coverage points with connectivity examples for all the components

- Consistency of interface, installation, operation, and documentation across all our VIPs

- Provide complete solutions and easy integration in IP and SoC environment

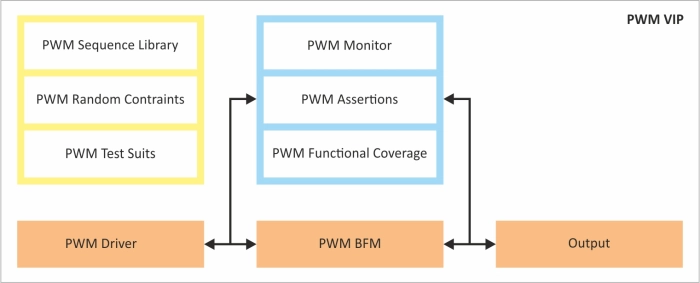

Block Diagram

Deliverables

- PWM Driver/BFM/Agent

- PWM Monitor

- Testbench Configurations

- Test Suite (Available in Source code)

- Basic and Directed Protocol Tests

- Random Tests

- Error Scenario Tests

- Assertions & Cover Point Tests

- Integration Guide, User Manual, and Release Note

Technical Specifications

Short description

PWM Verification IP

Vendor

Vendor Name