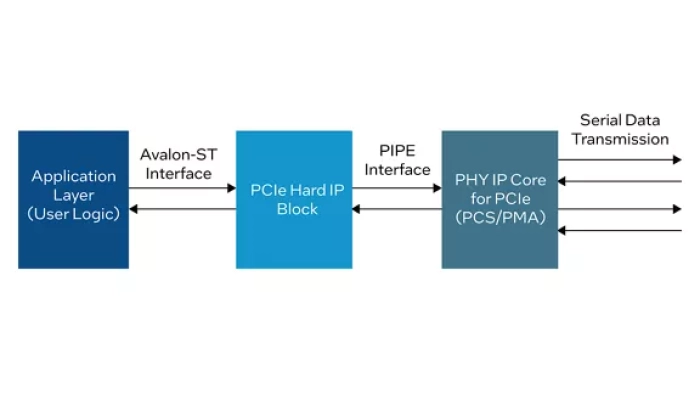

Intel® Arria® 10 and Intel® Cyclone® 10 GX FPGAs include a configurable, hardened protocol stack for PCI Express* that is compliant with the PCI Express Base Specification 3.0 and PCI Express Base Specification 2.0 respectively. The hard IP provides the Avalon® Streaming (Avalon-ST) interface and can be configured for either Rootport (RP) or Endpoint (EP) modes.

Complementary soft IPs are available for single root I/O virtualization (SR-IOV) support and bridging to an Avalon Memory Mapped interface (Avalon-MM) with DMA functionality.

Standards & Specifications Compliance

Intel Arria 10 PCIe Hard IP has successfully passed PCI-SIG compliance testing.