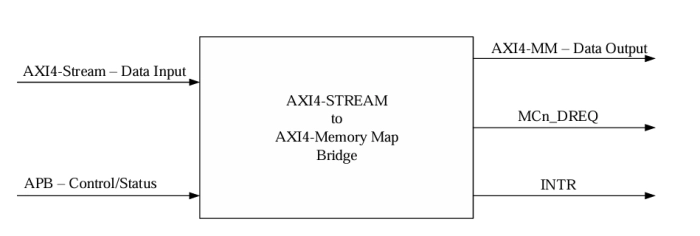

The DB-AXI4-STREAM-TO-AXI4-MM-BRIDGE Verilog RTL IP Core accepts AXI4-Stream data and control input, converts the control TID to a AXI4 Memory Map address, and signals a DMA Controller to read the data by way of a AXI4 Slave Memory Map read channel.

The DB-AXI4-STREAM-TO-AXI4-MM-BRIDGE IP Core works with the DMA Controller (i.e. the DB-DMAC-MC-AXI Verilog RTL IP Core) to transfer data from an AXI4-Stream peripheral or AXI4-Stream Network Interface to either memory or another peripheral.

The companion IP, the DB-AXI4-MM-TO-STREAM-BRIDGE, works with the vendor DMA Controller to transfers data from memory or a peripheral to an AXI4-Stream peripheral or AXI4-Stream Network Interface.