Arasan I3C PHY - Ternary vs. Non-Ternary

I3C (Improved Inter-Integrated Circuit) is a communication protocol that builds on the I2C standard, offering improved performance, power efficiency, and data rates. In the I3C PHY layer, ternary and non-ternary modes refer to the encoding methods used for signaling.

Ternary Mode

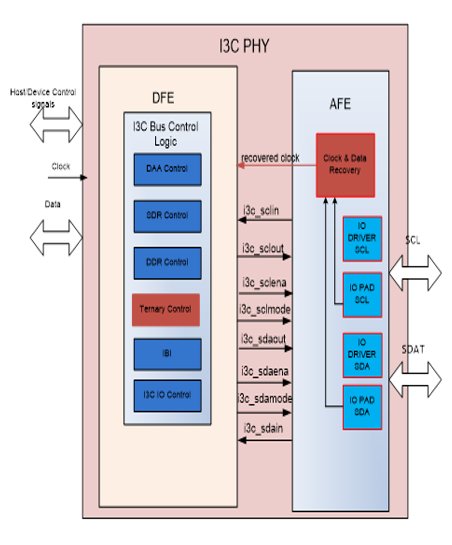

- Definition: In ternary mode, three signal states are used for communication. This allows more information to be encoded in fewer transitions. HDR-TSP and HDR-TSL use Ternary signaling on the two wires.

- Advantages:

- Higher Data Rates: By encoding more data per signal transition, ternary mode can achieve faster data transfer rates.

- Power Efficiency: It can be more power-efficient as fewer transitions are required to send the same amount of data.

- Noise Immunity: The intermediate state provides better noise tolerance, as small fluctuations in voltage may not result in misinterpreted signals.

- Applications: Ternary signaling is typically used in high-speed I3C communication where maximizing data throughput is important.

Non-Ternary Mode

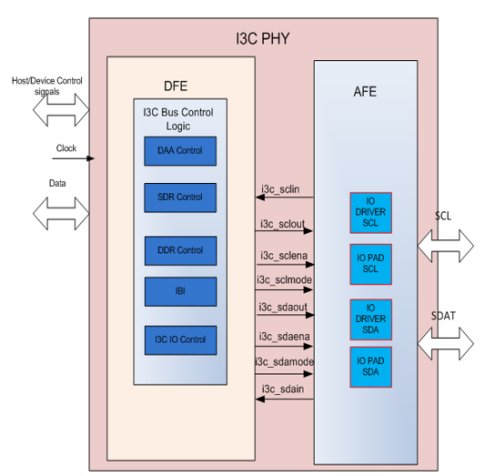

- Definition: Non-ternary mode refers to traditional binary signaling with two states. But no HDR-TSL/TSP support.

- Advantages:

- Simplicity: Easier to implement in hardware since it uses only two states (high and low).

- Compatibility: Works well with legacy I2C devices that only support binary signaling.

- Lower Complexity: Non-ternary mode may be easier to design and debug due to simpler signaling.

- Applications: Non-ternary mode is commonly used in lower-speed, lower-power applications where the simplicity of binary signaling is sufficient.

Key Differences

- Data Encoding:

- Ternary mode uses three states, allowing more data per transition.

- Non-ternary mode uses two states (binary signaling).

- Speed:

- Ternary mode offers higher data rates.

- Non-ternary mode operates at lower speeds.

- Complexity:

- Ternary mode is more complex to implement but more efficient.

- Non-ternary mode is simpler but less efficient in terms of data rate.

- Use Case:

- Ternary mode is typically used for high-performance devices requiring fast communication.

- Non-ternary mode is used in simpler, cost-sensitive, or legacy systems.

If you're designing or selecting an I3C PHY, the choice between ternary and non-ternary mode will depend on your application's speed, power efficiency, and hardware complexity requirements.

Related Semiconductor IP

Related Blogs

- Exploring the XSPI PHY: Technical Characteristics, Architectural Challenges, and Arasan Chip Systems' Solution

- I3C IP: Enabling Efficient Communication and Sensor Integration

- How Arasan’s SoundWire PHY Can Elevate Your Next Audio SoC

- Arasan’s xSPI/eMMC5.1 PHY: Unified Dual-Mode Physical Layer IP

Latest Blogs

- Considerations When Architecting Your Next SoC: NoCs with Arteris

- Implementing Dual-core Lockstep in the CHIPS Alliance VeeR EL2 RISC-V core for safety-critical applications

- Rethinking Display Safety: Why RISC-V-Supervised DisplayPort Subsystems Enable Secure, Isolated Automotive Architectures

- Area, Pipelining, Integration: A Comparison of SHA-2 and SHA-3 for embedded Systems.

- Why Your Next Smartphone Needs Micro-Cooling