Push-Button NoCs for SoCs

SoC 设计人员需要一个“一站式”工具来探索解决方案空间,并解决他们所有的互连挑战。

作者: Andy Nightingale

独特的实现挑战

当今的系统级芯片(SoC) 器件可能由数百个称为知识产权(IP)模块的功能块组成。这些IP中的每一个都可以包含数亿个晶体管。处理器、内存、编解码器和通信功能等标准 IP 通常可以从第三方供应商处获得。通过采购传统 IP,设计团队可以专注于内部开发特殊功能,例如用于人工智能(AI)和机器学习(ML)应用程序的推理引擎。这些内部开发的IP是将该SoC与竞争产品区分开来的“秘诀”。

在所有 IP 之间的通信方面,SoC 开发人员面临着独特的实现挑战。问题始于SoC行业已经定义和采用了多个接口协议(OCP,APB,AHB,AXI,STBus,DTL等)的事实,而每个IP可能采用不同的协议。此外,每个 IP 的接口可能具有不同的数据路径宽度和频率。传统的基于总线和交叉开关的实现无法处理现代 SoC 架构的复杂性。解决方案是使用片上网络(NoC)。许多人没有意识到的是,NoC是一个IP,尽管它跨越了整个SoC。

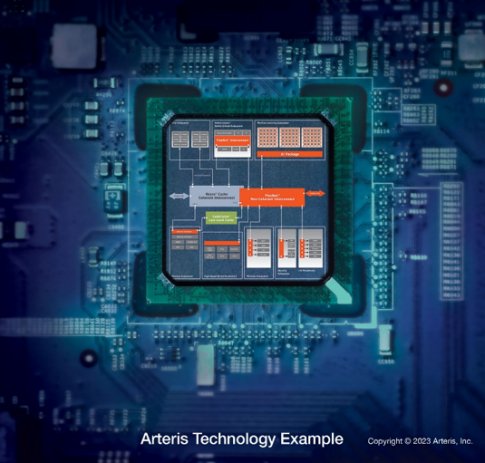

图片由Arteris, Inc.提供

套接字、开关、缓冲区和流水线寄存器

在 NoC之中,称为套接字的函数与每个 IP 接口相关联。每个套接字充当其 IP 和 NoC 之间的中介。一些 IP 充当发起者(数据生成器),而其他 IP 充当目标(数据接收者)。在许多情况下,同一 IP 可以在不同的时间承担这两个角色。在发起端,套接字会将 IP 的协议转换为通用的分组数据包和序列化传输机制。当数据包到达目的地时,目标的套接字会将其转换回目标 IP 支持的协议。

大量数据包可以同时传输。除了放置在相关 IP 块附近的套接字外,NoC 还涉及开关、缓冲区和流水线寄存器,它们的放置是一项由许多因素决定的复杂活动。

探索解决方案空间

大约在 1960 年代和 1970 年代,许多软件开发人员——尤其是那些创建了我们现在认为的嵌入式系统的前身的人——用称为汇编语言的低级符号代码捕获他们的程序。每个处理器都有自己的汇编语言,并且该语言中的助记符指令与处理器的底层指令集架构(ISA) 之间有很强的对应关系。

即使当 C 编程语言在 1970 年代中期开始出现时,许多使用微处理器单元 (MPU)和微控制器单元(MCU)的程序员仍然更喜欢使用汇编语言,因为他们相信生成的机器代码会运行得更快、更小、内存效率更高。

他们没有意识到的是,C程序员可以在很短的时间内创建相同的应用程序。这种速度的影响远远超出了工程师的生产率。用汇编语言编写的开发人员通常只有时间创建单个实现。这意味着,在考虑了手头的任务后,他们必须在第一时间选择最佳解决方案。相比之下,在C领域工作的程序员可以快速轻松地探索解决方案空间,创建、比较和对比各种实现,以确定每个应用程序的最佳解决方案。

同样的情况也适用于NoC的世界。一些开发团队决定逐个项目手工制作定制 NoC。除了耗时且容易出错之外,这意味着他们还必须同时调试和验证NoC和设计的其余部分。由于他们手动实现 NoC,因此他们需要预先做出某些架构决策。基础NoC拓扑应该是星形、环形、环面、树形、网格,还是它们的组合? 对于那些创建NoC的人来说,改变方向是非常困难的,并且在开发周期的后期纠正问题变得更具挑战性。

按钮式NoC

另一种方法是采用强大的、经过验证的、现成的第三方 NoC IP 解决方案,例如 Arteris IP 公司的事实上的行业标准 FlexNoC Interconnect IP。这被归类为“按钮式”互连IP,因为用户只需将IP块的数量和位置、所需的接口协议和所需的NoC拓扑通知FlexNoC GUI。使用此输入,只需按一下按钮即可以在寄存器传输语言(RTL)中生成相应的 NoC。

在探索解决方案空间时,FlexNoC独树一帜。假设用户已经指示 FlexNoC GUI 实现环形拓扑。下一步将是生成验证测试平台。同样,这也是一个按钮操作,因为FlexNoC系统已经可以访问所有必需的信息。在这种情况下,它将实例化事务处理器和目标,并使用它们生成所需的测试向量。

系统生成各种流量配置文件的能力与在 CPU 或 GPU IP 上运行代码不同。这些配置文件与运行单独应用程序的不同类型的 IP 相关联,例如在访问缓存时进行短时间读取和写入,或者在将纹理映射加载到 GPU 时进行长时间读取。

FlexNoC还支持自动插入探头,从而可以实时监控在NoC周围移动的所有数据包。来自测试平台的结果可以以图形“热图”的形式显示,表明任何拥塞点。

最初选择的环形拓扑可能不适合此应用。树结构会更好吗? FlexNoC具有很聪明的部分,因为IP块不会改变,这意味着相关的验证测试平台不需要改变。所需要做的就是指示 FlexNoC GUI 采用树形拓扑,只需按一下按钮即可生成新的 NoC 实现。

但是等等,还有更多!

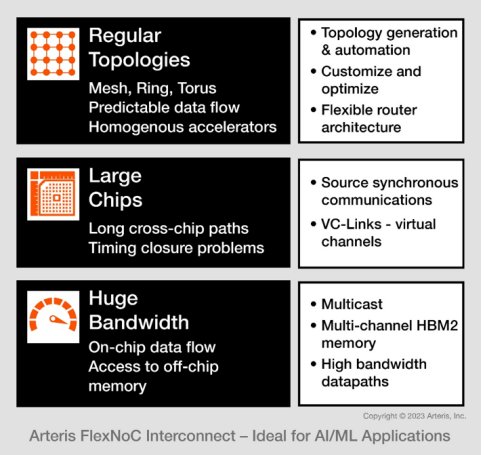

这里介绍的所有内容几乎没有涉及各种可能性。例如,同一 SoC 中可能有多个 NoC,而每个 NoC 都有自己的拓扑。比如,网格可用于多瓦片结构推理引擎,而在该SoC的其余部分使用分层树拓扑。选择源同步通信和虚拟通道(VC)链路以及广播组播数据包以适应极端带宽应用也是可行的。

高带宽链路可以短而宽,以促进吞吐量,而低带宽链路可以长而细,以最大程度减少拥塞。FlexNoC 支持灵活的电源域分区,可以关闭 NoC 未使用部分的电源,并允许智能时钟门控仅对主动处理数据包的逻辑进行计时,而不会引入任何额外的延迟。

图片由Arteris, Inc.提供

开发当今的 SoC 具有挑战性,但通过采用强大、经过验证的 NoC IP 解决方案可以降低复杂性。SoC 设计人员需要一个 “一站式” NoC 工具来探索解决方案空间,并解决他们所有的互连挑战。其解决方案之一是 Arteris IP的主要行业标准 FlexNoC interconnect IP。

Andy Nightingale是 Arteris IP公司产品营销副总裁,在高科技行业拥有超过35年的经验,其中包括在Arm担任多种工程和产品管理职位23年。

Andy Nightingale是 Arteris IP公司产品营销副总裁,在高科技行业拥有超过35年的经验,其中包括在Arm担任多种工程和产品管理职位23年。