Other

All offers in

Other

Filter

Compare

8

Other

from

5

vendors

(1

-

8)

-

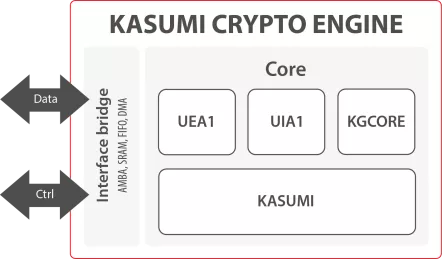

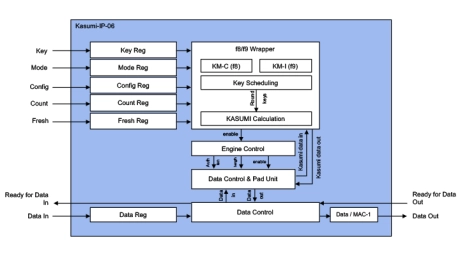

KASUMI Crypto Engine

- The KASUMI IP core is 3GPP confidentiality and integrity algorithms (UEA1/UIA1) stream cipher for telecommunication applications, requiring high performance with reduced silicon resources.

- It is optimized for maximum throughput and minimum latency.

-

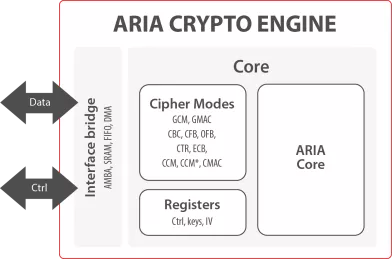

ARIA Crypto Engine

- The ARIA crypto engine includes a generic implementation of the ARIA algorithm which is the block cipher standard of South Korea.

- It is compliant with the RFC 6209 specification and can support several cipher modes including authenticated encryption.

-

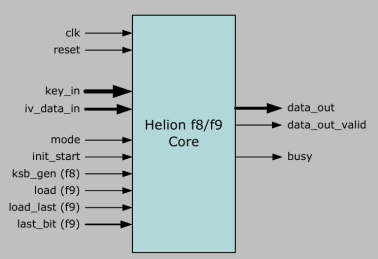

3GPP KASUMI f8 and f9 cores

- The Helion 3GPP KASUMI cores perform the f8 confidentiality and f9 integrity algorithms required to provide data security within the GSM/EDGE and UMTS mobile communication standards.

- Both algorithms are based on the KASUMI 64-bit block cipher which uses a 128-bit key. The KASUMI algorithm was designed by the Security Algorithms Group of Experts (SAGE) within ETSI, and is an optimised version of the MISTY1 block cipher originally developed by Mitsubushi Electric Corporation of Japan. Within ETSI, the f8 and f9 algorithms are now known as UEA1 and UIA1 respectively.

-

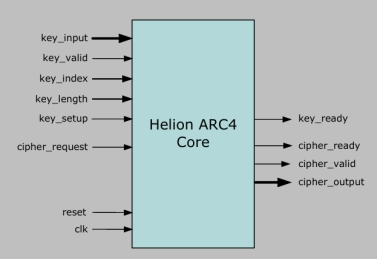

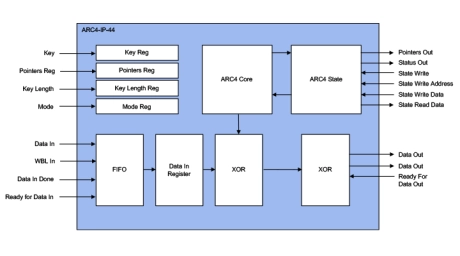

ARC4 Core for Xilinx FPG

- The Helion ARC4 core implements the Alleged RC4 stream cipher algorithm. The RC4 algorithm itself was developed by Ron Rivest in 1987 and was originally a trade secret of RSA Security. However, a description of the algorithm became widely available on the Internet in 1994 and so the algorithm is no longer considered a trade secret, although the name RC4 itself is still trademarked.

- Legal third party implementations are therefore often referred to as Alleged RC4, which is usually abbreviated to ARC4.

-

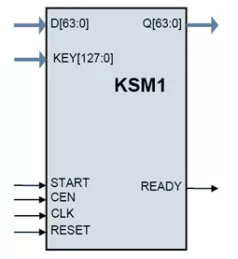

3GPP Kasumi Accelerators

- Wide bus interface (64-bit data, 128-bit keys) or 32-bit register interface.

- Includes key scheduling hardware.

- Modes Kasumi

- Algorithms f8 and f9.

- Fully synchronous design.

- Low Speed, High Speed versions.

-

Kasumi Encryption Core

- Encryption using the Kasumi Block Cipher Algorithm

- Since all practical uses of Kasumi utilize only the encryption operation, decryption is not part of the core

- High throughput: up to 3 Gbps in 65 nm process

- Small size: from 5.5K ASIC gates

-

ARC4 Stream Cipher Accelerators

- The ARC4-IP-44 (EIP-44) is IP for accelerating the ARC4 stream cipher algorithm (used for legacy SSL & IPsec) up to 5 Gbps @ 600MHz.

- Designed for fast integration, low gate count and full transforms, the ARC4-IP-44 accelerator provides a reliable and cost-effective embedded IP solution that is easy to integrate into high-speed crypto pipelines.

-

GOST (Kuznyechik Cipher) Core

- Supports all cipher modes defined in NIST SP800-38A: ECB, CBC, CFB1, CFB8, CFB128, OFB and CTR.