ChaCha20-Poly1305 IP

All offers in

ChaCha20-Poly1305 IP

Filter

Compare

9

ChaCha20-Poly1305 IP

from

5

vendors

(1

-

9)

-

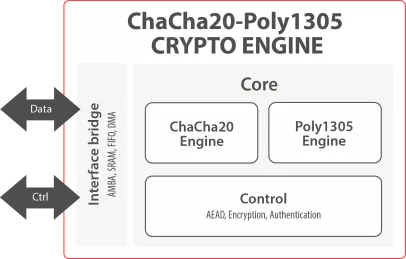

ChaCha20-Poly1305 Crypto Engine

- Fully compliant with RFC7539

- Supports encryption/decryption only (Chacha20)

- Supports authentication only (Poly1305)

-

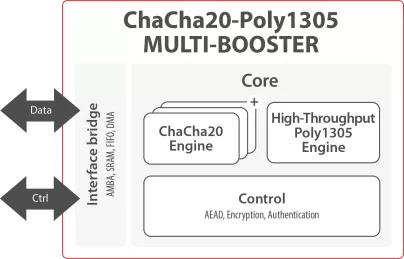

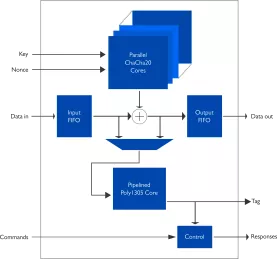

Chacha20-Poly1305 Multi-Booster

- The ChaCha20-Poly1305 Multi-Booster Crypto Engine is RFC7539 compliant to provide Authenticated Encryption with Associated Data (AEAD) using the ChaCha20 stream cipher combined with the Poly1305 message-authentication code.

-

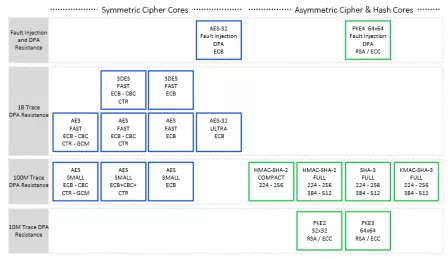

ChaCha20 DPA Resistant Crypto Accelerator

- Quicken time-to-market using precertified DPA Countermeasures

- Highly secure cryptographic engine primitives

- Extensive validation using the Test Vector Leakage Assessment (TVLA) methodology (revealing no leakage beyond 100 million traces)

- Cores protected against univariate first- and second-order side-channel attacks beyond 1 billion operations

-

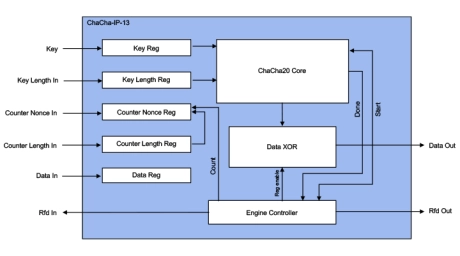

ChaCha20 Accelerators

- The ChaCha-IP-13 (EIP-13) is an IP solution for accelerating the ChaCha20 cipher algorithm (RFC7539), supporting the NIST CTR mode up to 12.8 Gbps @ 300MHz.

- Designed for fast integration, low gate count and full transforms, the ChaCha-IP-13 accelerator provides a reliable and cost-effective embedded IP solution that is easy to integrate into high-speed crypto pipelines.

-

High-Speed IP Core for ChaCha20-Poly1305 Authenticated Encryption

- Moderate resource requirements

- Performance

- High Throughput with Short Latency

-

ChaCha20 stream cipher core

- Simple register based interface

- Processing of 64-bytes in as low as 13 clock cycles

- Selection between High Throughput or Low Gate-Count architectures

- Real-time selection between key generation or cipher/decipher modes

-

Combined ChaCha20 and Poly1305 core

- Multiple processing modes:

- Chacha20 processing of 64-bytes in as low as 13 clock cycles

- Poly1305 processing of 16-bytes in as low as 4 clock cycles

- Different processing architectures offering different balances between throughput/area

-

Chacha20-Poly1305 IP for FPGA and ASIC

- Available in 2 versions:

- Fast : High bandwith with low latency and high frequency

- Small : Higher latency but smaller footprint

- Full standard support : Zyxx ChaCha20-Poly1305 supports full specification of the ChaCha20-Poly1305 standard

-

Balanced IP Core for ChaCha20-Poly1305 Authenticated Encryption

- Moderate resource requirements

- Performance

- High Throughput with Short Latency