High-Speed IP Core for ChaCha20-Poly1305 Authenticated Encryption

XIP2113H from Xiphera is a high-speed Intellectual Property (IP) core designed for ChaCha20-Poly1305 Authenticated Encryption wit…

Overview

XIP2113H from Xiphera is a high-speed Intellectual Property (IP) core designed for ChaCha20-Poly1305 Authenticated Encryption with Associated Data (AEAD) scheme protecting both confidentiality and authenticity at the same time. The current definitive standard for ChaCha20-Poly1305 is RFC 8439, “ChaCha20 and Poly1305 for IETF Protocols”.

ChaCha20-Poly1305 is a combination of the ChaCha20 stream cipher and Poly1305 message authentication code, both algorithms designed by Daniel J. Bernstein, and it is used an AEAD scheme in multiple protocols, including TLS 1.3.

XIP2113H has been designed for easy integration with FPGA- and ASIC-based designs in a vendor-agnostic design methodology, and the functionality of XIP2113H does not rely on any FPGA manufacturer-specific features.

Key features

- Moderate resource requirements: The entire XIP2113H requires 14928 Adaptive Lookup Modules (ALMs) (Intel Agilex F). Contact sales@xiphera.com for ASIC resource requirements.

- Performance: XIP2113H achieves a throughput in the tens of Gbps range, for example 33.75+ Gbps in Intel Agilex F. Even higher throughputs can be achieved with parallel instantiations of XIP2113H.

- High Throughput with Short Latency: XIP2113H offers very high throughput for a single stream of data as it is capable to process one 16-byte block per clock cycle after certain initial latency. The length of the initial latency depends on the length of the message and XIP2113H has been carefully optimized to minimize this initial latency.

- Constant Latency: The execution time of XIP2113H is independent of the key values and message contents (apart from the message length), and consequently provides full protection against timing-based side-channel attacks.

- Standard Compliance: XIP2113H is fully compliant with RFC 8439 “ChaCha20 and Poly1305 for IETF Protocols”.

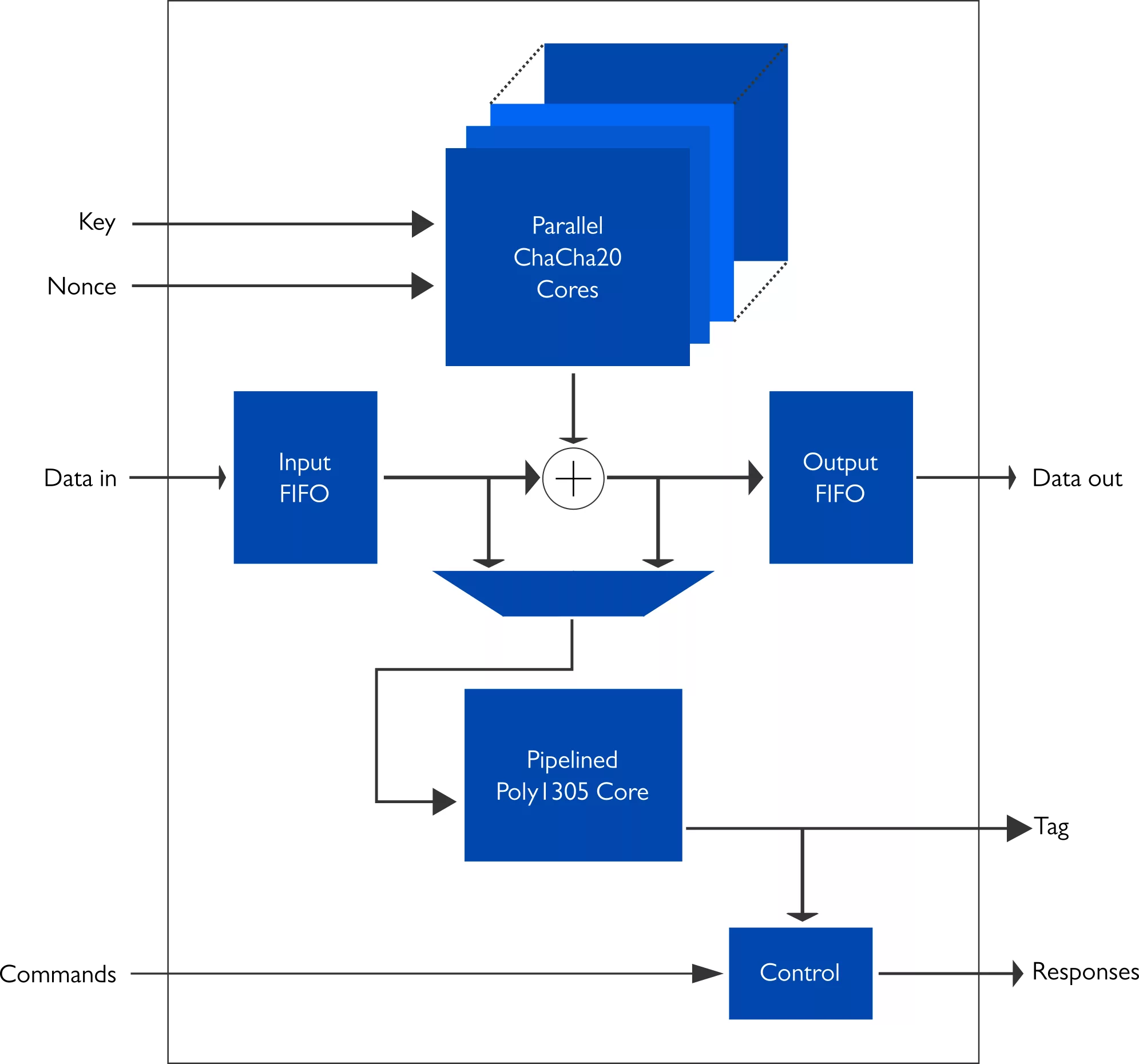

Block Diagram

Benefits

- Fully digital design

- Portable to any ASIC or FPGA technology

- Fully standard compliant

- Easy to integrate

- Several bus interfaces available

- IP core designed in-house at Xiphera

- Technical support by the original designers and cryptographic experts

Applications

- TLS 1.3, WireGuard VPN protocol.

What’s Included?

- Please contact sales@xiphera.com for pricing and your preferred delivery method. XIP2113H can be shipped in a number of formats, including netlist, source code, or encrypted source code.

- Additionally, synthesis scripts, a comprehensive testbench, a high-level Python model, and a detailed datasheet including an integration guide are included.

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Symmetric Crypto IP core

CXL - The Latest Specification in Secured Network Traffic

Securing your apps with Public Key Cryptography & Digital Signature

RoT: The Foundation of Security

Tailoring Root Of Trust Security Capabilities To Specific Customer Needs

Symmetric Cryptographic Offload Options for SoC Designers

Frequently asked questions about Symmetric Cryptography IP cores

What is High-Speed IP Core for ChaCha20-Poly1305 Authenticated Encryption?

High-Speed IP Core for ChaCha20-Poly1305 Authenticated Encryption is a Symmetric Crypto IP core from Xiphera Ltd listed on Semi IP Hub.

How should engineers evaluate this Symmetric Crypto?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Symmetric Crypto IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.