ML-DSA

ML-DSA IP cores (Modular Lattice-based Digital Signature Algorithm IP cores) are advanced cryptographic hardware blocks designed to deliver post-quantum security and high-performance digital signature operations for modern embedded systems, FPGAs, and ASICs. Built to comply with the NIST PQC standardization for digital signatures, ML-DSA IP cores offer a secure and efficient alternative to traditional algorithms such as RSA or ECDSA, which are vulnerable to quantum attacks.

Explore our vast directory of ML-DSA IP cores below.

All offers in

ML-DSA

Filter

Compare

29

ML-DSA

from

12

vendors

(1

-

10)

-

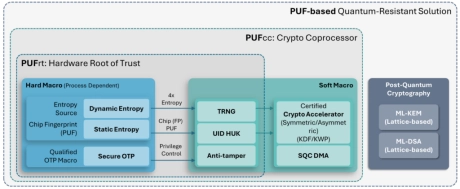

PUF-based Post-Quantum Cryptography (PQC) Solution

- PUFsecurity is proud to pioneer the world’s first PUF-based Post-Quantum Cryptography (PQC) solution, delivering cutting-edge, hardware-level security that sets a new standard.

- Our innovative solution integrates PUF technology with quantum-resistant cryptographic algorithms, ensuring robust key protection and seamless transition to a quantum-secure future.

-

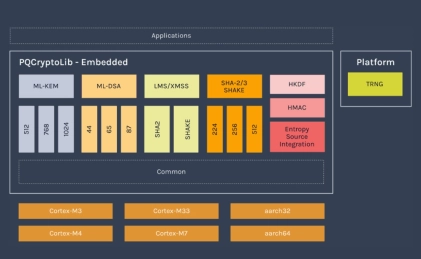

Highly-optimized PQC implementations, capable of running PQC in under 15kb RAM

- PQCryptoLib-Emebedded is a versatile, CAVP-ready cryptography library designed and optimized for embedded devices.

- With its design focused on ultra-small memory footprint, PQCryptoLib-Embedded solutions have been specically designed for embedded systems, microcontrollers and memory-constrained devices. It provides a PQC integration to devices already in the field.

-

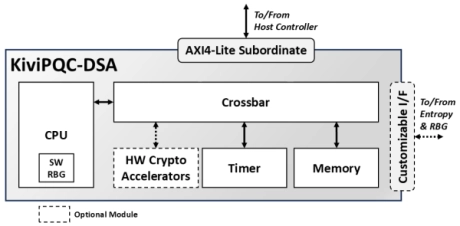

ML-DSA Digital Signature Engine

- The KiviPQC™-DSA is a hardware accelerator for post-quantum cryptographic operations.

- It implements the Module Lattice-based Digital Signature Algorithm (ML-DSA), standardized by NIST in FIPS 204.

- This mechanism realizes the appropriate procedures for securely generating a private/public key pair, digitally signing a message or a data block, and performing digital signature verification.

-

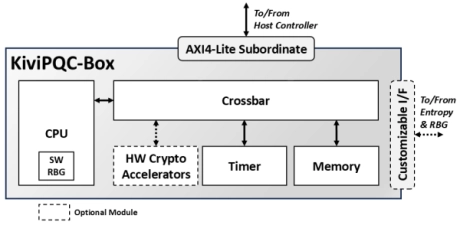

ML-KEM Key Encapsulation & ML-DSA Digital Signature Engine

- The KiviPQC™-Box is a hardware accelerator for post-quantum cryptographic operations.

- It implements both the Module Lattice-based Key Encapsulation Mechanism (ML-KEM) and the Module Lattice-based Digital Signature Algorithm (ML-DSA), standardized by NIST in FIPS 203 and FIPS 204, respectively.

-

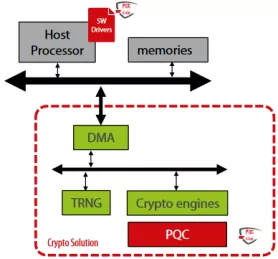

Crypto Coprocessor with integrated Post-Quantum Cryptography IPs

- The Crypto Coprocessors are a hardware IP core platform that accelerates cryptographic operations in System-on-Chip (SoC) environment on FPGA or ASIC.

- Symmetric operations are offloaded very efficiently as it has a built-in scatter/gather DMA. The coprocessors can be used to accelerate/offload IPsec, VPN, TLS/SSL, disk encryption, or any custom application requiring cryptography algorithms.

-

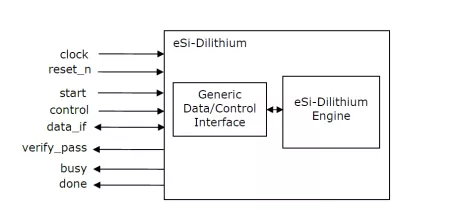

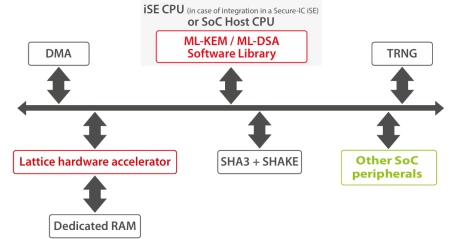

ML-KEM / ML-DSA Post-Quantum Cryptography IP

- ML-KEM (Crystals-Kyber) and ML-DSA (Crystals-Dilithium) are Post-Quantum Cryptographic (PQC) algorithms, meaning they are mathematically designed to be robust against a cryptanalytic attack using a quantum computer.

- Both have been standardized by the NIST in it post-quantum cryptography project.

-

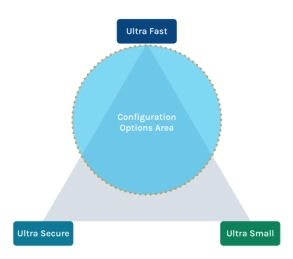

Single instance HW Lattice PQC ultra accelerator

- PQPerform-Flare is a powerful hardware-based FIPS 140-3 CAVP-certified product, designed for high throughput and low latency PQC.

- It adds PQC for applications that typically handle a large number of transactions, such as high-capacity network hardware applications and secure key management HSMs.

-

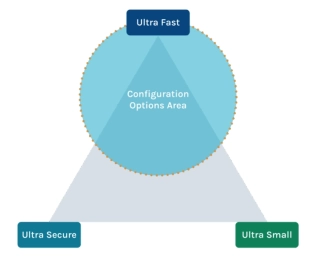

Highly configurable HW Lattice PQC ultra acceleration in AXI4 & PCIe systems

- PQPerform-Inferno is a powerful, scalable hardware solution engineered for unparalleled performance in the post-quantum era.

- As a FIPS 140-3 CAVP-certified product, it provides a trusted foundation for next-generation security.

-

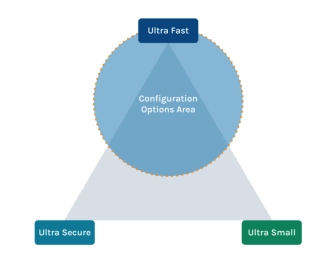

PQPerform-Inferno + RISC-V processor for enhanced crypto-agility

- PQPerform-Flex provides robust and agile high-performance acceleration for the ML-KEM and ML-DSA post-quantum cryptographic algorithms but also future standards (programmable post-silicon, such as HQC), designed for seamless integration into modern SoC designs for both ASIC and FPGA targets.

-

CRYSTALS Dilithium core for accelerating NIST FIPS 204 Module Lattice Digital Signature algorithm

- Hardware core for accelerating the high-level operations specified in the NIST FIPS 204 standard.