ultra-low voltage memory IP

Filter

Compare

15

IP

from

8

vendors

(1

-

10)

-

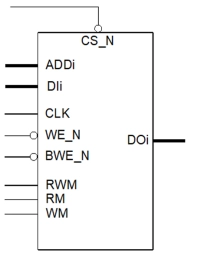

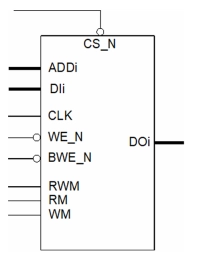

Single Port Low Voltage SRAM Memory Compiler on N22ULL - Low Power Retention and Column Repair

- Ultra-Low Leakage: High VT (HVT) are used to minimize leakage performance

- Bit Cell: Utilizes Low Leakage 6T bit cells to ensure high manufacturing yields

- Ultra Low Power Standby: Internally generated bias voltage for low leakage data retention

- Isolated Array and Periphery supplies: Periphery voltage can be shut off to further reduce standby power

-

Single Port Low Voltage SRAM Memory Compiler on N22ULL

- Ultra-Low Leakage: High VT (HVT) are used to minimize leakage performance

- Bit Cell: Utilizes Low Leakage 6T bit cells to ensure high manufacturing yields

- Ultra Low Power Standby: Internally generated bias voltage for low leakage data retention

-

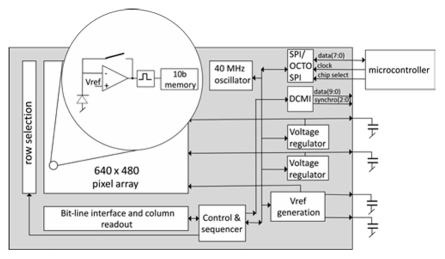

Ultra-low power high dynamic range image sensor

- Resolution: VGA (640 x 480)

- Backside illuminated sensor

- Pixel size: 6.3 μm x 6.3 μm

- Fill factor: 83 %

- Dynamic range: 120 dB intra-scene

-

Single Port High Speed SRAM Memory Compiler on N22ULL

- Ultra low power data retention. Memory instances generated by the Bulk 22ULL go into a deep sleep mode that retains data at minimal power consumption.

- Self biasing. The SP SRAM 22ULL internal self-biasing capabilities provide ease of IP integration.

- High yield. To ensure high manufacturing yield, bulk 22ULL uses low leakage 6T (0.110µ2) bit cells and is consistent with Design for Manufacturing (DFM) guidelines for the Bulk 22ULL process.

- High usability. All signal and power pins are available on metal 4 while maintaining routing porosity in metal 4. Power pins can optionally be made available on metal 5 to simplify the power connections at the chip level.

-

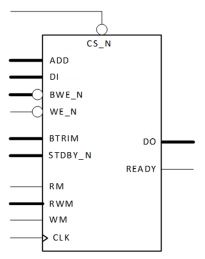

Single Port Low Leakage SRAM Memory Compiler on GF 22FDX

- Ultra-Low Leakage: High VT (HVT) and low leakage (LLHVT) devices are used with source biasing to minimize standby currents while operating at low voltage

- Bit Cell: Utilizes GlobalFoundries® Ultra-Low Leakage 6T (P110UL) bit cells to ensure high manufacturing yields

- Five Power Modes: High Performance, Low Leakage, Standby, Retention, and Power Off modes provide flexibility for power optimization

- Speed Grades: Three options to adjust the speed/leakage balance and optimize for high speed or low power operation

-

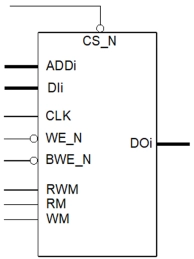

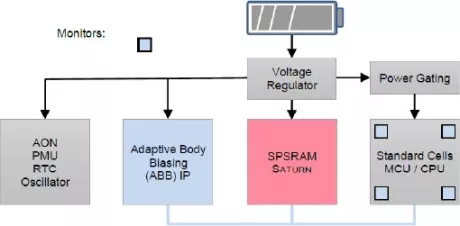

Low Power Memory Compiler - 1-Port Register File Compiler - GF 22nm FDX

- Specifically designed for ultra-low power applications, this memory leverages body biasing to dramatically reduce power consumption.

- Compatible with industry Adaptive Body Biasing IP for PVT and aging compensation

- Body Biasing functionality (up to +1.3V / -1.5V) to reduce leakage or increase speed at the same power

-

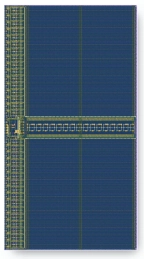

Single Rail SRAM GLOBALFOUNDRIES 22FDX

- Ultra-low voltage logic designs using adaptive body biasing demand dense SRAM solutions which fully integrate in the ABB aware implementation and sign-off flow of the Racyics® ABX Platform solution.

- The Racyics® Single Rail SRAM supports ultra-low voltage operation down to 0.55 V where logic designs with Minimum-Energy-Point are implemented.

-

Dual Rail SRAM Globalfoundries 22FDX

- Single port SRAM compiler based on P124 bitcell with Dual-supply-rail architecture

- Bitcell array supply voltage 0.8V and ULV core interface down to 0.4V enabled with Racyics' ABB

-

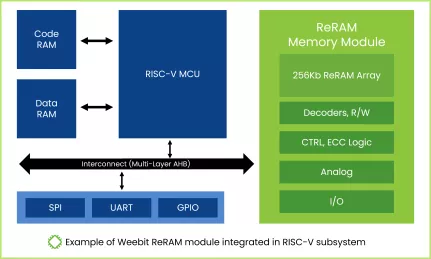

ReRAM NVM in SkyWater 130nm

- Weebit Resistive RAM (ReRAM) is a new type of Non-Volatile Memory (NVM) that is designed to be the successor to flash memory.

- Weebit ReRAM IP can provide a high level of differentiation for System-on-Chip (SoC) designs, with performance, power, cost, security, environmental, and a range of additional advantages compared to flash and other NVMs.

- Weebit’s first ReRAM IP product is available now in SkyWater Technology’s 130nm CMOS process (S130). The technology is fully qualified, available for integration in SkyWater’s users’ SoCs, and ready for production.

-

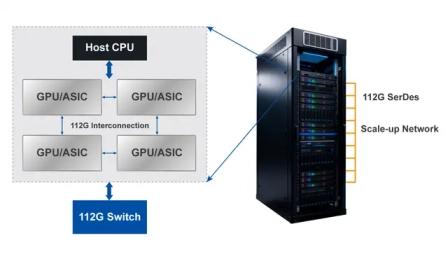

112G Multi-SerDes

- Designed with a small footprint, ultra-low latency, and low power consumption, the 112G SerDes maximizes bidirectional memory access efficiency, reduces software complexity, and helps chip developers leverage existing Ethernet infrastructure to significantly lower Total Cost of Ownership (TCO).

- Featuring IEEE 802.3-compliant Forward Error Correction (FEC), 35dB ultra-high channel loss compensation, and adaptive high-speed equalization technologies (CTLE, FFE), it provides full-cycle link protection—from error correction to pre-warning—enabling highly compatible, stable, and efficient chip-to-chip connectivity solutions.