ultra low power PLL IP

Filter

Compare

34

IP

from

11

vendors

(1

-

10)

-

Ultra low Power High Speed 150MHz integer-N PLL IP Core

- Integer Division

- High Stability

- Designed to be power-efficient

- Low Jitter

-

Ultra low Power High Speed 400MHz lnteger-N PLL IP Core

- Integer Division

- High Stability

- Designed to be power-efficient

- Low Jitter

-

Ultra low Power High Speed 500MHz integer-N PLL IP Core

- Integer Division

- High Stability

- Designed to be power-efficient

- Low Jitter

-

Ultra low Power High Speed 600MHz lnteger-N PLL IP Core

- Integer Division

- High Stability

- Designed to be power-efficient

- Low Jitter

-

Ultra low Power High Speed 800MHz Frac-N PLL IP Core

- Designed to be power-efficient

- Fractional Division

- High Resolution of 800MHz

- Low Jitter

-

Ultra low Power 1.4GHz Frac-N PLL IP Core

- Designed to be power-efficient

- Fractional Division

- High Resolution of 1.4GHz

- Low Jitter

-

Ultra Low-Power High-Performance AFE on GF 22FDX

- The ODT-AFE-2T2R-GF22FDX is an ultra-highperformance AFE designed in a Global Foundries 22nm process.

- The AFE includes two 12-bit, 4GSPS I/Q ADC pairs, two 14-bit, 8GSPS I/Q DAC pairs, four capless LDOs, one Bandgap reference and one temperature sensor and includes an integrated 3rd party PLL.

-

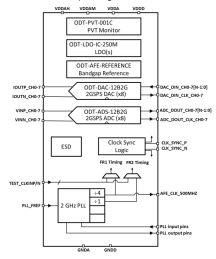

Ultra Low-Power High-Performance AFE in 12nm

- The ODT-AFE-1T1R-12 is an ultra-high-performance AFE designed in a 12nm process.

- The AFE includes 1 IQ Pairs of Tx and Rx for either the FR1 or FR2 band. This is comprised of two 12-bit 2GSPS ADCs, and two 12-bit 2GSPS DACs.

- This AFE also includes multiple capless LDOs, a voltage/current reference, and a low jitter 2 GHz PLL

-

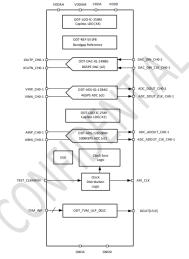

Ultra Low-Power High-Performance AFE on 12nm

- The ODT-AFE-4T4R-12nm is an ultra-high-performance AFE designed in a 12nm CMOS process.

- The AFE includes 2 IQ Pairs of Tx and Rx for the FR2 band, and combines them with 2 additional IQ Pairs of Tx and Rx for the FR1 band clocked at a lower sample rate.

-

8 Channels, 12 bit, 2GS/s Swift™ ADCs, and 4 Channels, 12 bit, 200 MS/s Swift™ ADC with Integrated PLL

- The ODT-AFE-12A1P2T-16FFCT is an ultra highperformance AFE designed in a 16nm CMOS process.

- The AFE includes eight 12-bit, 2GSPS ADCs, four 12-bit 200MSPS ADCs, two TV monitors, multiple LDOs for ADC supplies, and a low jitter fractional-N PLL.