standard cell libraries IP

Filter

Compare

100

IP

from

15

vendors

(1

-

10)

-

Standard Cell Libraries GF 55nm

- The Standard Cell libraries deliver thousands of highly optimized cells with each one being optimized for power, area, speed, routing, and yield.

- These libraries may be extended with Power Management Kits, taking power reduction to the next level, and ECO Kits to enable late-stage design modifications.

-

Standard Cell Libraries - GLOBALFOUNDRIES 22FDX

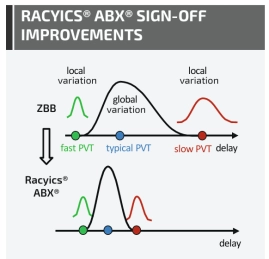

- Body biasing is a disruptive 22FDX® feature which enables the adaption of transistor threshold voltages after production during device operation.

- Racyics® dense 9T logic standard cells libraries and low power 8T standard cell libraries are fully enabled for the adaptive body biasingaware implementation and sign-off flow of the Racyics® ABX® Platform solution.

-

Standard Cell Library

- Basic Cells: A full suite of fundamental logic gates and flip-flops.

- Optimal Cells: High-performance variants of basic cells, optimized for power, area, and speed, including high-speed flip-flops, advanced multiplexers, clock gated cells, clock buffers, arithmetic cells and custom-designed cells for critical paths.

-

Standard Cell Library, Low Voltage Operation 0.45 V TSMC N3P

- Nominal voltage of 0.75 V +/-10 %

- Low voltage of 0.45 V +/-10 %

- Track height: 7.5T

- Operating temperature: -40°C to 125°C

-

Standard Cell

- Dolphin offers an extensive array of Standard Cell libraries that have been methodically tested and verified in silicon for each process technology supported.

- More than 3500 fully customizable cells are available, and each has been optimized for speed, routability, power and density, in order to maximize performance and wafer yield while lowering overall SoC cost.

-

Standard Cell Library in TSMC (12nm~180nm)

- -Ultra-High-Density Standard Cell Library (HDSC) for highest density, lowest cost and lowest power

- -General Purpose Standard Cell Library (GPSC) for general purpose logic with balanced PPA

- -Ultra-High Speed Standard Cell Library (HSSC) for the optimized performance in the critical path

- -Low Leakage Standard Cell library (LLSC) for ultra-low-leakage

-

9 track standard cell library at TSMC 55 nm

- Compromise for density and speed

- 9-Track high cells

- Only Metal 1 used for cell design

- Compatible with 1P3M SoC implementation

-

9 track standard cell library at TSMC 55 nm

- Compromise for density and speed

- 9-Track high cells

- Only Metal 1 used for cell design

- Compatible with 1P3M SoC implementation