pll IP

Filter

Compare

2,852

IP

from

103

vendors

(1

-

10)

-

5 GHz 150 fs Jitter PLL - GlobalFoundries 22nm

- Input Frequency: ~100MHz, ~200MHz

- Output Frequency: 5 GHz

- RMS Jitter: <150 fs

- Supply Voltages: 0.8 V, 1.8V

-

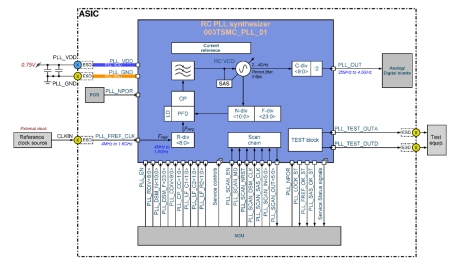

25MHz to 4.0GHz Fractional-N RC PLL Synthesizer on TSMC 3nm N3P

- Fractional-N Phase locked loop frequency synthesizer is intended for ASIC clock generation.

- The Fractional-N PLL loop with 2GHz-4GHz VCO has high phase noise performance and ultra-fine frequency tuning step.

- VCO Sub-band auto select (SAS) system allows to find automatically appropriate sub-band for VCO on locked PLL.

-

Integer-N PLL, 600M-2.4G on SMIC 40nm

- This present IP is a self-biased Phase Locked Loop (PLL) circuit, which can cover 600MHz-2.4GHz vco output frequency

- It can generate adjustable clock from input signal by change the dividers’ value

- There are two same post dividers following vco with ratio 1, 2, 4, 8, 16.

-

Integer-N PLL, 32M ~ 256MHz on UMC 55nm

- This present IP is a Phase Locked Loop (PLL) circuit

- It’s analog PLL suitable for various frequency node generations

- The VCO can run from 32MHz to 256MHz

- It contains input clock divider (DIVM), a feedback clock divider (DIVN) and level shifter block to switch signals between VDD12 and VDD33

-

Integer-N PLL, 800M-3.2G on TSMC 12nm

- This present IP is a charge-pump Phase Locked Loop (PLL) circuit, which can cover 800MHz-3200MHz vco output frequency

- It consists blocks of M divider, PFD, charge pump, low pass filter, VCO and lock detector

- It can generate adjustable clock with the integer-N value.

-

5 GHz 250 fs Jitter PLL - GlobalFoundries 22nm

- The PLL5G250F is an ultra-low power phase locked loop (PLL) intellectual property (IP) block.

- The PLL5G250F features a very small area footprint, with exceptional jitter performance in its power/area class and flexible programmability, making this IP ideal for a wide range of general purpose clocking and specialized applications.

-

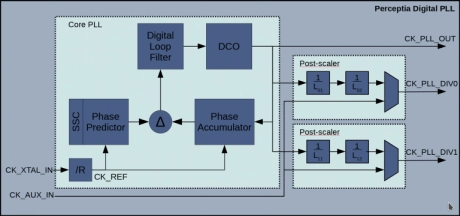

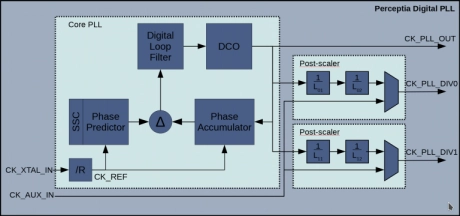

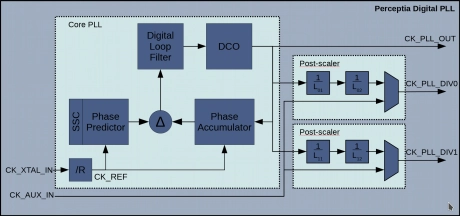

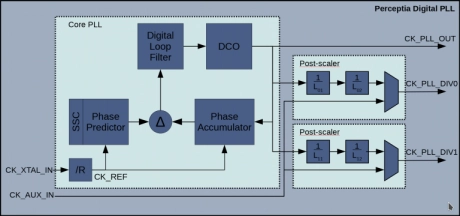

General Purpose All Digital Fractional-N PLL in UMC 40LP

- Low jitter (< 18ps RMS)

- Small size (< 0.01 sq mm)

- Low Power (< 3.5mW)

- Support for multi-PLL systems

-

Low Power All Digital Fractional-N PLL in TSMC N6/N7

- Low power, suitable for IoT applications

- Good jitter, suitable for clocking digital logic.

- Extremely small die area (< 0.005 sq mm), using a ring oscillator

- Output frequency can be from 1 to 400 times the input reference, up to 1.5GHz

-

Low Power All Digital Fractional-N PLL in Samsung 14LPP

- Low power, suitable for IoT applications

- Good jitter, suitable for clocking digital logic.

- Extremely small die area (< 0.005 sq mm), using a ring oscillator

- Output frequency can be from 1 to 400 times the input reference, up to 1.5GHz

- Reference clock from 5MHz to 200MHz

-

Low Power All Digital Fractional-N PLL in GlobalFoundries 12LPP/14LPP

- Low power, suitable for IoT applications

- Good jitter, suitable for clocking digital logic.

- Extremely small die area (< 0.005 sq mm), using a ring oscillator

- Output frequency can be from 1 to 400 times the input reference, up to 1.5GHz

- Reference clock from 5MHz to 200MHz