imaging vision processor IP

Filter

Compare

7

IP

from

4

vendors

(1

-

7)

-

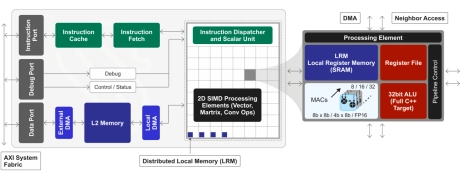

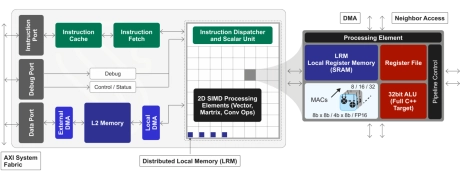

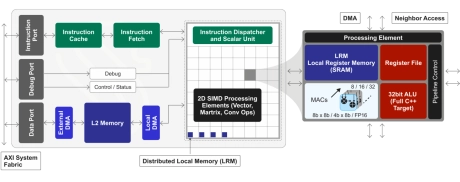

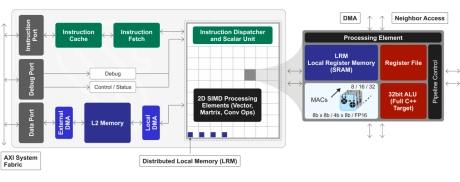

GPNPU Processor IP - 32 to 864TOPs

- 32 to 864TOPs

- (Dual, Quad, Octo Core) Up to 256K MACs

- Hybrid Von Neuman + 2D SIMD matrix architecture

- 64b Instruction word, single instruction issue per clock

- 7-stage, in-order pipeline

- Scalar / vector / matrix instructions modelessly intermixed with granular predication

-

-

-

-

Deep Learning Processor

- High performance: Whether it’s at the edge or in the cloud, videantis' processors provide the required performance.

- Scalable architecture: 1 to 1000+ cores address ultra-low cost to high-performance applications.

- Ultra-high MAC throughput: Each core computes a high number of MACs per cycle, resulting in an abundant amount of processing performance in multi-core systems.

-

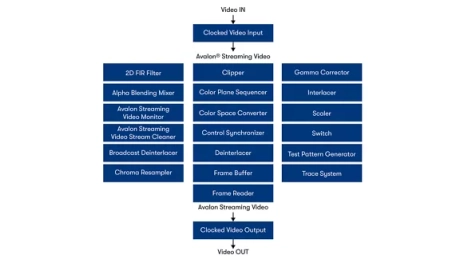

Video and Image Processing Suite

- The Intel FPGA Video and Image Processing Suite is a collection of Intel FPGA intellectual property (IP) functions that you can use to facilitate the development of custom video and image processing designs

- These Intel FPGA IP functions are suitable for use in a wide variety of image processing and display applications, such as studio broadcast, video conferencing, AV networking, medical imaging, smart city/retail, and consumer.

-

MIPI CSI-2 IP

- The MIPI CSI-2 IP core is a highly scalable and silicon-agnostic implementation of the MIPI Camera Serial Interface 2 version 4.1 targeting ASIC and FPGA technologies.

- The MIPI CSI-2 implementation enables high-speed, low-power transmission of image data from camera modules to host processors.