image cognition IP

Filter

Compare

29

IP

from

14

vendors

(1

-

10)

-

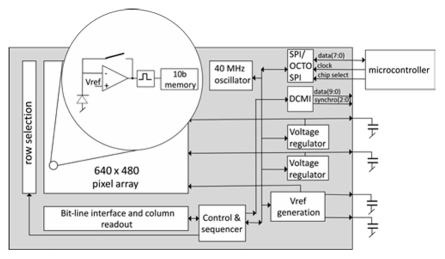

Ultra-low power high dynamic range image sensor

- Resolution: VGA (640 x 480)

- Backside illuminated sensor

- Pixel size: 6.3 μm x 6.3 μm

- Fill factor: 83 %

- Dynamic range: 120 dB intra-scene

-

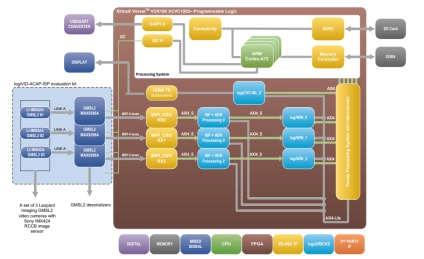

ACAP HDR Image Signal Processing Framework

- The ACAP HDR Image Signal Processing Framework is intended to showcase a complete logicBRICKS IP suite implementation of High-Dynamic Range (HDR) Image Signal Processing (ISP) pipeline in an embedded design based on AMD-Xilinx ACAP programmable devices.

- The HDR ISP pipeline enables crisp camera video under altering and rough lighting conditions in next generation multi-channel embedded systems for use in automotive, surveillance, medical, aerospace and similar video and vision AI applications.

-

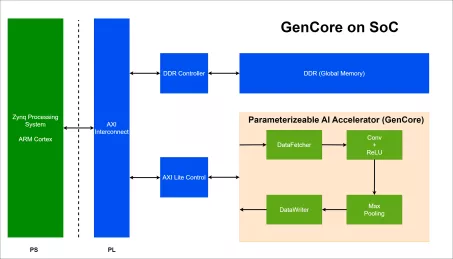

AI Accelerator Specifically for CNN

- A specialized hardware with controlled throughput and hardware cost/resources, utilizing parameterizeable layers, configurable weights, and precision settings to support fixed-point operations.

- This hardware aim to accelerate inference operations, particulary for CNNs such as LeNet-5, VGG-16, VGG-19, AlexNet, ResNet-50, etc.

-

Visibility Improver IP

- Improves the visibility in various shooting conditions.

- Supports both AXI4-stream I/F and DE (data enable) I/F as input/output video interface.

- Selectable starting by software or hardware event.

-

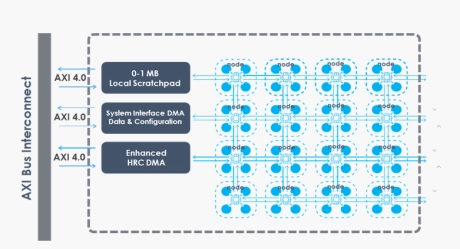

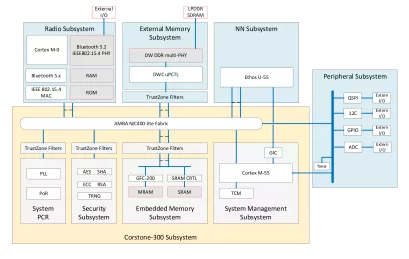

IP platform for intelligence gathering chips at the Edge

- High performance IoT solutions for AI at the Edge can now be created up to 30% faster

-

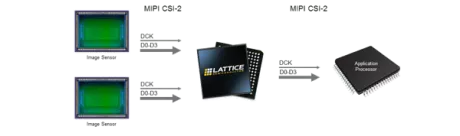

Two Input to One Output MIPI CSI-2 Camera Aggregator Bridge

- Supports MIPI CSI-2 inputs and outputs at up to 6 Gbps

- Combines two MIPI CSI-2 inputs to one MIPI CSI-2 output

- Supports all CSI-2 data types

- Compliance with MIPI D-PHY Specification v1.1

-

Four Input to One Output MIPI CSI-2 Camera Aggregator Bridge

- Supports MIPI CSI-2 inputs and outputs at up to 6 Gbps: 1, 2 or 4 Data Lanes

- Merges two of four MIPI CSI-2 inputs to one MIPI CSI-2 output

- Supports all CSI-2 data type: RAW, RGB, YUV

- Compliance with MIPI D-PHY Specification v1.1

-

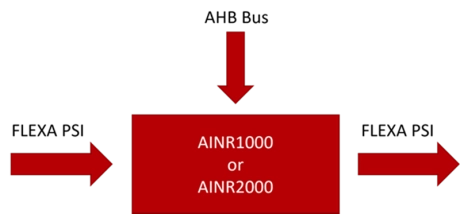

Cost-efficiency, AI-based noise reduction IP

- The AI-NR series IPs offer noise reduction solutions for optimizing image quality in low-light or complex lighting conditions.

- Currently consisting of the AINR1000 and AINR2000 IPs, this series is capable of significantly reducing image noise while preserving rich picture details and color fidelity, providing superior performance for optimizing image quality in low-light or complex lighting conditions.

- With dynamic noise processing technology, the AINR1000 efficiently handles not only static noise but also motion noise in video, ensuring clear and smooth visuals at all times.

-

Neuromorphic Processor IP (Second Generation)

- Supports 8-, 4-, and 1-bit weights and activations

- Programmable Activation Functions

- Skip Connections

- Support for Spatio-Temporal and Temporal Event-Based Neural Network