eCPRI IP

Filter

Compare

9

IP

from

5

vendors

(1

-

9)

-

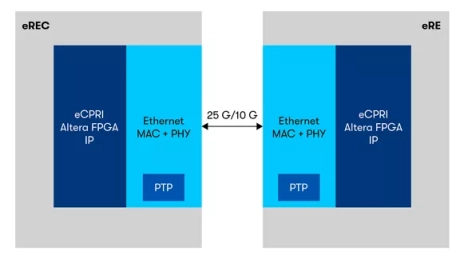

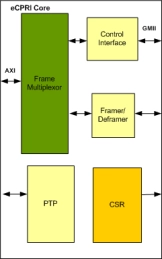

eCPRI Altera® FPGA IP

- The enhanced Common Public Radio Interface (eCPRI) Altera® FPGA IP core implements the eCPRI specification version 2.0

- It is a front-haul interface protocol for radio base stations aimed at connecting the eCPRI Radio Equipment Control (eREC) and the eCPRI Radio Equipment (eRE) via front-haul transport network.

-

eCPRI

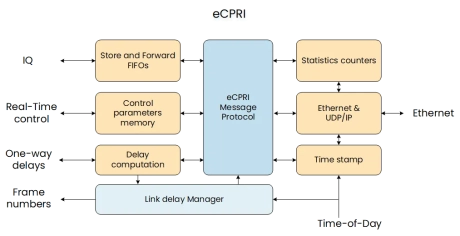

- eCPRI core is a highly scalable and silicon agnostic implementation of the eCPRI standard targeting any ASIC or FPGA technologies.

- The eCPRI implementation builds on Chip Interfaces long-time experience designing CPRI and Radio-Over-Ethernet solutions for fronthaul and delivers a flexible engine that is prepared for tight integration with software applications.

-

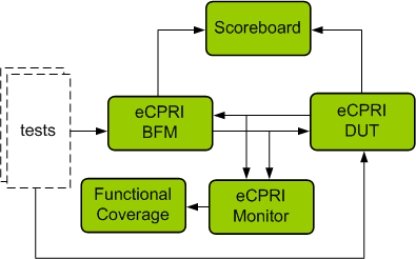

eCPRI Verification IP

- Compliant with eCPRI Specification V2.0.

- Complete eCPRI Tx/Rx functionality.

- Supports the eCPRI layer of the eCPRI specification.

- Supports 5G and enables increased efficiency.

-

eCPRI Controller IIP

- Compliant with eCPRI Specification v2.1

- Supports complete eCPRI Tx/Rx Functioanlity

- Supports various Ethernet Speeds - 10G/25G/40G/100G

- Supports rich configuration to handle multi mode wireless systems

-

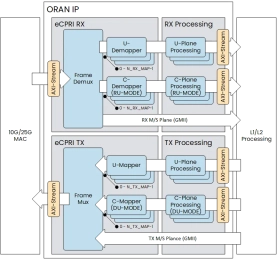

ORAN IP core

- ORAN IP core is a highly scalable and silicon agnostic implementation of the interoperable O-RAN WG4 defined 7.2x interface for deployment in O-DU and O-RU products, targeting any ASIC, FPGA or ASSP technologies.

- The ORAN over eCPRI implementation builds on long-time experience designing CPRI and Radio-Over-Ethernet solutions for fronthaul and delivers a flexible engine that is prepared for tight integration with software applications.

-

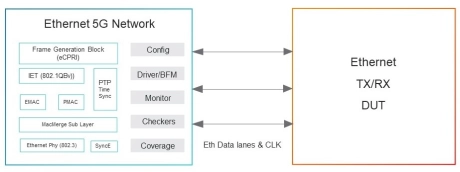

Simulation VIP for Ethernet 5G Network

- SyncE

- Supports clock generation from transmit side

- Supports Hold-off and Wait-to-restore feature

- Support for 25G speed with serial interface

-

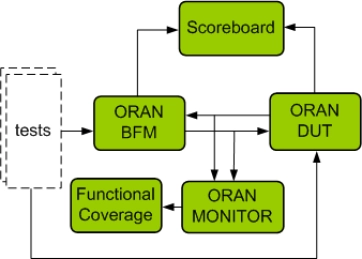

ORAN Verification IP

- Compliant with ORAN Specification V6.0.

- Complete ORAN Tx/Rx functionality.

- Supports O-RU and O-DU

- Supports the below encapsulation

-

56G-LR Pam4 SerDes PHY

- Supports Ethernet, FC, CPRI, and eCPRI protocols

- Compliant to IEEE 802.3ck and OIF standard electrical specifications

- Supports 56Gbps PAM4 and 28G, 10G, and sub-10Gbps NRZ data rates

- Unique firmware-controlled adaptive power design provides optimal power and performance tradeoffs and more efficient system designs based on platform requirements

- Continuous calibration and adaption provide robust performance across process, voltage, and temperature

- Supports industrial temperature range -40°C – 125°C

-

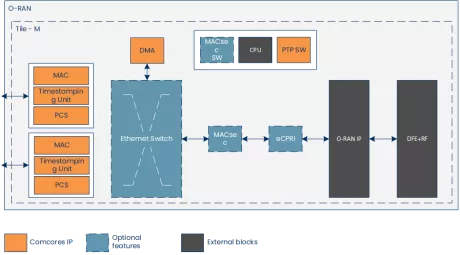

O-RAN Fronthaul Transport Subsystem

- HW validated packaged IP solution

- The pre-integrated IP solution consists of building blocks, which are integrated

and tested together. - Reduces customer’s time to market and risk Frees up customer’s strategic resources

- The IP blocks can be combined in a flexible way to suit customer’s requirements