chip monitor IP

Filter

Compare

194

IP

from

42

vendors

(1

-

10)

-

TSMC CLN12FFC Chip Performance Monitor

- TSMC 12nm 0.8V/1.8V CMOS Logic FinFET Compact Process

- Metal Scheme: 1P7M (2Xa1Xd_h_3Xe_vhv) or above

- Support one clone critical path ring oscillator customization

- Maximum 32 internal ring oscillators

-

TSMC CLN7FF Chip Performance Monitor

- Supports one clone critical path ring oscillator customization

- Maximum 32 internal ring oscillators

- Supply voltage range: -20 % to +50 %, from 0.6 V to 1.125 V

- (Typ. 0.75 V)

-

TSMC CLN5FF Chip Performance Monitor

- TSMC 5 nm 0.75 V/1.2 V CMOS LOGIC FinFET Process

- Metal scheme: 1P16M (1X_h_1Xb_v_1Xe_h_1Ya_v_1Yb_h_4Y_vhvh_2Yy2Yx2R) or above

- Support one clone critical path ring oscillator customization

- Maximum 32 internal ring oscillators

-

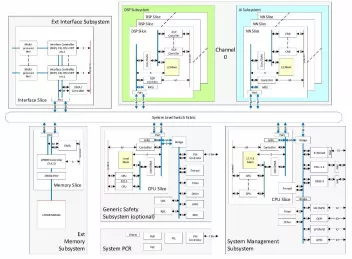

Single channel ADAS chip with FuSa monitor

- The SFA 250A has been designed to be easy to adapt to suit the support needs of the customer’s IP as it is scalable, both in terms of function and performance, as well as modular as multiple versions can be combined to form larger solutions.

-

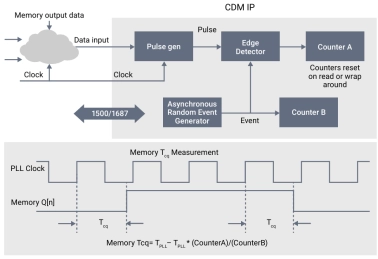

SLM Clock & Delay Monitor IP

- The SLM Clock & Delay Monitor (CDM) IP can be implemented in silicon with minimal area overhead. It doesn’t need any accurate high speed reference clock and provides accurate time delay measurement.

- It can be used for measuring clock duty cycle, memory access time, delay line characteristics, etc. It has IEEE 1500/1687 interface for connecting to test fabric.

- The SLM CDM IP is also available as an ISO 26262 ASIL-B ready product.

-

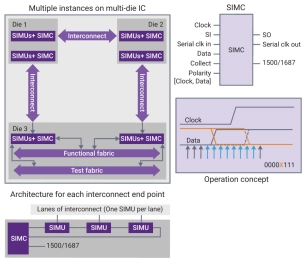

SLM Signal Integrity Monitor

- The SLM Signal Integrity Monitor (SIM) IP enables signal quality measurement for die-to-die interfaces. It can be implemented in silicon with minimal area overhead. It enables accurate measurement of silicon interconnects with real-time reporting for analytics.

- With the use of Monitor, Test and Repair (MTR), this real-time reporting enables structural lane monitoring, aging related degradation, and optional repair of failing lanes to maintain high-speed performance throughout the silicon lifecycle.

-

UFS Hardware Validation Platform (HVP)

- Compliant to JEDEC UFS 1.0, HCI 1.0, UniPro 1.40

- Available in Host and Device configuration

-

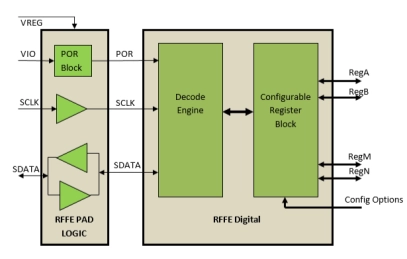

RFFE Slave IP Core

- Compliant with MIPI’s RFFE specification Rev 3.0

- Small silicon footprint

- Scalable Implementation

- Up to 15 Devices can be connected per Bus

- Low pin count on Interface side (SCLK and SDATA)

-

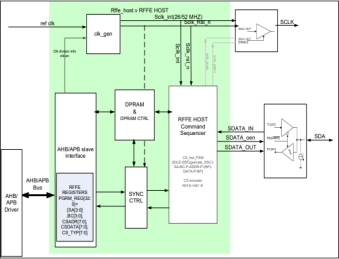

RFFE Master IP Core

- Compliant with MIPI RFFE Specification 3.0

- Delivered in Reuse Methodology Manual (RMM) compliant Verilog RTL format

- Optionally delivered as a physical design

- Small footprint