Video Deinterlacer IP

Filter

Compare

23

IP

from

8

vendors

(1

-

10)

-

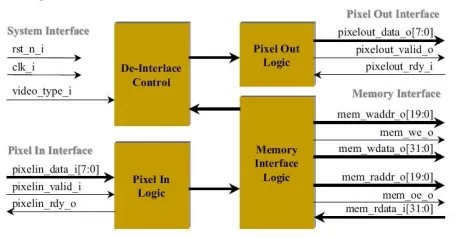

Video DeInterlacer

- Supports PAL or NTSC video mode

- RAM like memory interface with separate read and write controls

- Fully stallable interfaces on both input and output

-

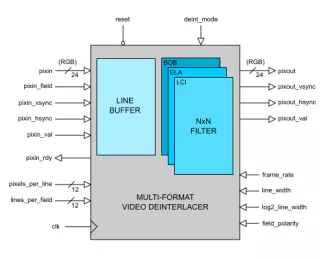

DO-254 Multi-Format Video Deinterlacer 1.00a

- 24-bit RGB digital video throughout

- - Supports all interlaced digital video formats

- - Resolutions up to 4096x4096 pixels

- - Proprietary (LCI) de-interlacing algorithm

-

Video Deinterlacer

- Supports a wide range of industry standard video encoding and packing methods, including:

- Supports highly scalable resolutions from 128x128 up to 2048x2048, such as:

- Supports progressive pass through, "Progressive Segmented Frames" (PSF) and "Pull down" encoded streams

- Highly configurable and can be optimized for the smallest FPGA footprint

-

Multi-format Video Deinterlacer

- The DEINTERLACER IP Core is a high quality 24-bit RGB video deinterlacer capable of generating progressive output video at up to 4096x4096 pixels in resolution.

- The design is fully customizable, supporting any desired interlaced video format.

-

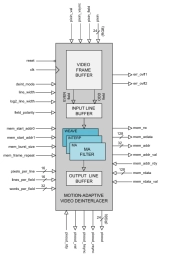

Motion-adaptive Video Deinterlacer IP Core

- The DEINTERLACER_MA IP Core is a studio quality 24-bit RGB video deinterlacer capable of generating progressive output video at any resolution up to 216 x 216 pixels.

- The design is fully programmable and supports any desired interlaced video format.

-

Standard Definition Video (PAL/NTSC) De-Interlacer, Basic Algorithm

- Deinterlaces standard 4:2:2 interlaced video streams into 4:2:0 raster streams.

- Spatial predictor and two-dimensional interpolation filter produces very high image quality.

- Directly connects to 8-bit, 4:2:2 interlaced video source

- Video format support includes either BT.656 or raw input with HSYNC,VSYNC timing.

-

Standard Definition Video (PAL/NTSC) De-Interlacer, Advanced Algorithm

- Deinterlaces standard 4:2:2 interlaced video streams into 4:2:0 raster streams.

- Advanced pixel-based, motion-adaptive algorithm produces very high image quality.

- Directly connects to 8-bit, 4:2:2 interlaced video source

- Video format support includes either BT.656 or raw input with HSYNC,VSYNC timing.

-

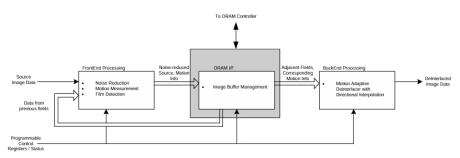

Video Processor and Deinterlacer with Line-Doubled Output

- The VPC-1 is a high quality motion adaptive deinterlacer and video processor with line-doubled output.

- Additional functions include motion adaptive noise reduction, low angle directional interpolation and film cadence detection (supports multiple cadences including 3:2, 2:2 and others).

-

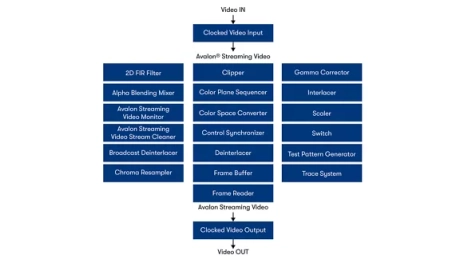

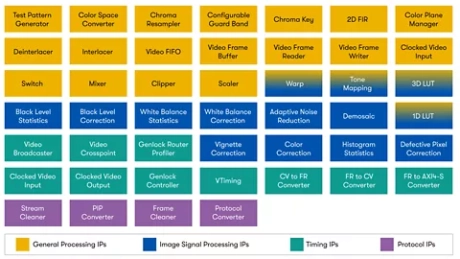

Video and Vision Processing Suite

- The Intel® FPGA Video and Vision Processing Suite is a collection of next-generation Intel® FPGA intellectual property (IP) functions that you can use to facilitate the development of custom video and image processing designs

- These Intel® FPGA IP functions are suitable for use in a wide variety of image processing and display applications, such as studio broadcast, video conferencing, AV networking, medical imaging, industrial inspections and robotics, smart city/retail and consumer.

-

Video and Image Processing Suite

- The Intel FPGA Video and Image Processing Suite is a collection of Intel FPGA intellectual property (IP) functions that you can use to facilitate the development of custom video and image processing designs

- These Intel FPGA IP functions are suitable for use in a wide variety of image processing and display applications, such as studio broadcast, video conferencing, AV networking, medical imaging, smart city/retail, and consumer.