USB3.0 OTG controller IP

Filter

Compare

5

IP

from

4

vendors

(1

-

5)

-

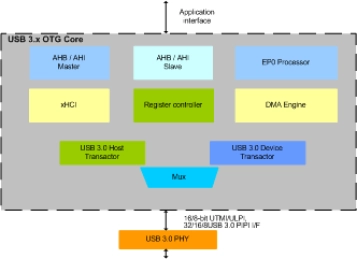

USB3.x OTG IIP

- USB 3.0/3.1/3.2 Common support

- Compliant with USB 3.0/3.1/3.2 specification

- Supports Superspeed USB 3.0, SuperSpeedPlus 3.1, 3.2

- Configurable number of Configurations, Interfaces, Alternative Interfaces and Endpoints

-

Simulation VIP for USB

- Configurations

- Gen2x2, Gen1x2, Gen2x1, and Gen1x1

- Supported DUT Models

- Host, Device and PHY Model for USB2 or USB3

-

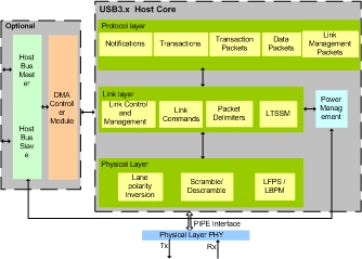

USB3.x HOST IIP

- USB 3.0/3.1/3.2 Common support

- Compliant with USB 3.0/3.1/3.2 specification

- Supports Superspeed USB 3.0, SuperSpeedPlus 3.1, 3.2 and 3.0 OTG

- Configurable number of Configurations, Interfaces, Alternative Interfaces and Endpoints