UFS 4.0 IP

Filter

Compare

16

IP

from

8

vendors

(1

-

10)

-

UFS 4.0 Host

- UFS 4.0 (JESD220F.pdf)

- UFS HCI 4.0 (JESD223E.pdf)

- MIPI UniPro version 2.0(mipi_UniPro_specification_v2-0.pdf)

- MIPI M-PHY version 5.0(mipi_M-PHY_specification_v5-0.pdf)

-

UFS 4.0 G5 Host Controller with IE and Unipro

- Compliant with the JEDEC UFS, UFSHCI v4.0 and UFS card v1.1 standards

- Enables data and privacy protection using Inline Encryption (AES-XTS) and RPMB

- Delivered as UFS host application layer integrated with Synopsys MIPI UniPro v2.0 Controller IP

- Manages UFS protocol between host and external UFS device

-

UFS 4.0 G5 Host Controller and Unipro

- Compliant with the JEDEC UFS, UFSHCI v4.0 and UFS card v1.1 standards

- Enables data and privacy protection using Inline Encryption (AES-XTS) and RPMB

- Delivered as UFS host application layer integrated with Synopsys MIPI UniPro v2.0 Controller IP

- Manages UFS protocol between host and external UFS device

-

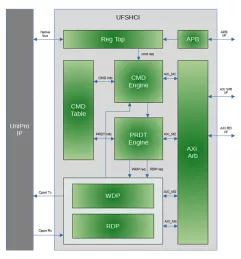

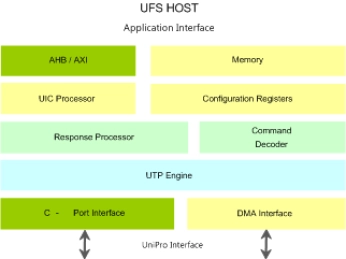

UFSHCI 4.0 - UFS Host Controller Interface

- Compliant with JEDEC UFSHCI Standard version 4.0 specification

- Compliant with JEDEC UFS Standard version 4.0 specification

- Up to 32 doorbells for UTP transfers

- Up to 32 Multi-Circular Queue (MCQ) UTP transfer requests

-

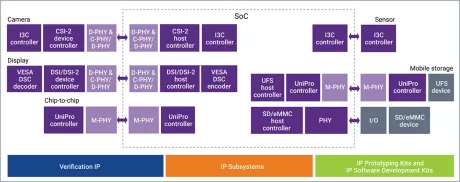

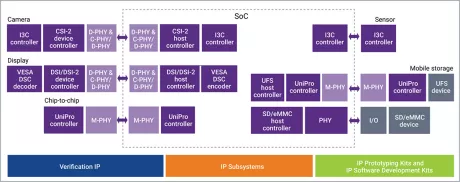

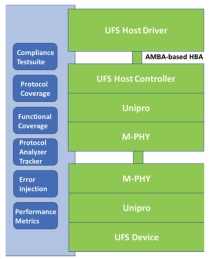

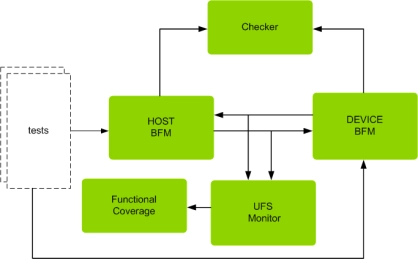

Verification IP for UFS

- Avery UFS/Unipro VIP provides a comprehensive verification solution featuring an advanced UVM environment that incorporates: constrained random SCSI and Unipro traffic generation, robust packet and physical layer controls and error injection, protocol checks and coverage, functional coverage, protocol analyzer-like features for debugging, and performance analysis metrics.

-

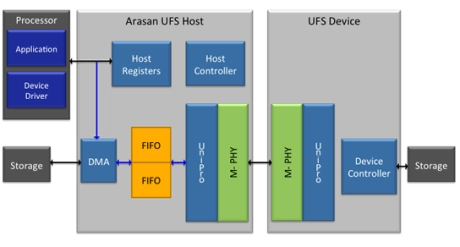

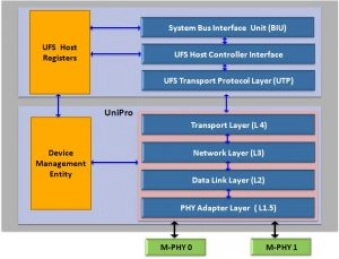

UFS 3.0 Host

- UFS 3.0 Host and Device configurations available

- Complete UFS 3.0 hardware implementation

- Interop-proven UniPro 1.8 link layer

- MIPI M-PHY 4.0 Interface

-

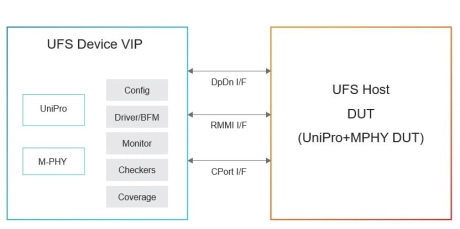

Simulation VIP for UFS

- Interfaces

- DPDN I/F and RMMI I/F when used with UniPro VIP. CPort signaling pin I/F and CPort message using transactions

- UTP Layer - UPIUs

- NOP IN, NOP OUT, Query Request/ Response, Task Management Request/ Response, Command, Response, Data Out, Data In

-

UFS Verification IP

- Full UFS Host and Device functionality.

- Compliant testsuite as per JESD224 document.

- Supports high performance M-PHY type-1

- Supports full UFS Host and Device functionality.

-

UFS HOST Controller IIP

- Supports high performance M-PHY type-1.

- Supports full UFS Host functionality.

- Supports UFS driver layer over UniPro.

- Supports configurable cport.

-

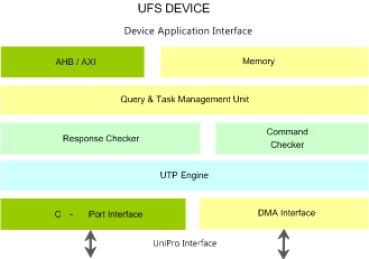

UFS DEVICE IIP

- Supports high performance M-PHY type-1.

- Supports full UFS Device functionality.

- Supports UFS driver layer over UniPro.

- Supports configurable cport