Static Memory Controller IP

Filter

Compare

85

IP

from

17

vendors

(1

-

10)

-

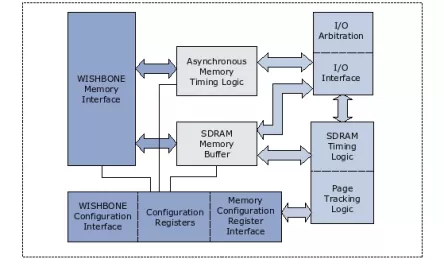

General Memory Controller

- The GMC (General Memory Controller) includes two memory controllers: The NOR/PSRAM memory controller, The Synchronous DRAM (SDRAM/Mobile LPSDR SDRAM) controller

-

PSRAM Memory Controller IP

- DFSPI – SPI FLASH Controller with Execute in place – XIP (SINGLE, DUAL and QUAD SPI Bus Controller with DDR / DTR support and optional AES Encryption) + … NOR & NAND Flash Memory Support

-

HYPERBUS™ Memory Controller

- The HyperBus™ Memory Controller IP Core is a high-speed, fully configurable SPI master/slave solution, designed for seamless integration into modern SoC and FPGA architectures.

- Building on the proven DFSPI core, this IP bridges easily to APB, AHB, and AXI buses, supporting SINGLE, DUAL, QUAD, and OCTAL SPI modes for maximum design flexibility.

-

-

DDR Memory Controller IP for low power and high reliability

- Supports DDR protocol standard JESD79F Specification.

- Compliant with DFI-version 2.0 or higher Specification.

- Supports all the DDR commands as per the specs. Supports up to 16 AXI ports with data width upto 512 bits.

- Supports controllable outstanding transactions for AXI write and read channels

-

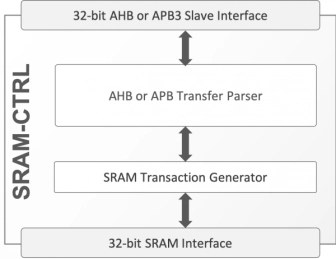

Static RAM Controller

- The SRAM-CTRL implements a Static Random Access Memory (SRAM) Controller translating AHB, or AXI4, or APB bus reads and writes into reads and writes with the signaling and timing of a standard 32-bit synchronous SRAM.

- The type of host interface is user-defined at synthesis time.

-

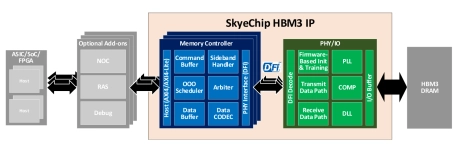

High Bandwidth Memory 3 (HBM3/3E) IP optimized for Samsung SF4X

- The HBM3 IP consists of a PHY and memory controller optimized for Samsung SF4X process to support the HBM3 memory standard (JESD238A) operating at up to 9.6 Gbps/pin.

- The HBM3 IP is designed for high memory throughput and low latency applications while minimizing area and power consumption.

-

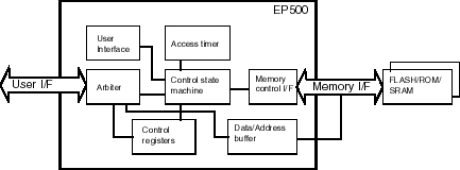

Flash/ROM/SRAM Controller

- Supports industry standard Asynchronous SRAM, NOR Flash, ROM and similar memory devices.

- Two request ports to allow two requesters to share access to the FLASH/ROM/SRAM devices.

- 8 Chip select signals to access up to 8 memory banks.

- Independent programmable timing parameters for each chip select.

-

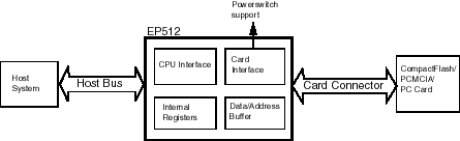

CompactFlash/PCMCIA Host Controller with EXCA Registers

- Compliant with PC Card Standard 8.0, PCMCIA 2.1/JIEDA 4.2 and CompactFlash 1.4.

- Allows host CPU to access CompactFlash, PC Card/PCMCIA devices.

- 82365SL-compatible register set, EXCA compatible.

-

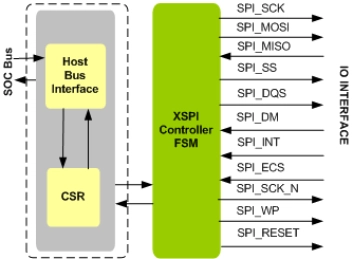

XSPI Controller IIP

- Compliant with XSPI protocol of JEDEC standard version 1.0 specification

- Support single master and multiple slaves per interface port

- Support source synchronous clocking

- Support Deep power down enter and exit commands