Silex Inside IP

Filter

Compare

226

IP

from

46

vendors

(1

-

10)

-

EdDSA Curve25519 signature generation engine

- The EdDSA Curve25519 extension adds hardware support for modern elliptic-curve cryptography inside DCD-SEMI’s configurable cryptographic co-processor.

- The implementation is based on Curve25519, a widely adopted 255-bit elliptic curve designed for efficient key exchange and digital signatures, with strong resistance to side-channel attacks and high performance in constrained embedded environments.

-

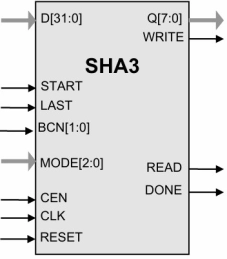

SHA3 Cryptographic Hash Cores

- Completely self-contained; does not require external memory

- SHA3-224, SHA3-256, SHA3-384, and SHA3-512 support SHA-3 algorithms per FIPS 202.

- SHAKE128 / SHAKE256 XOF support is included.

- Flow-through design; flexible data bus width

-

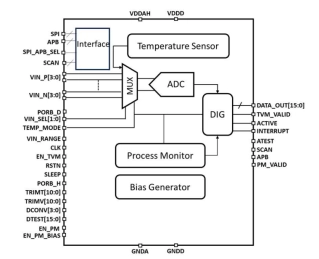

Ultra-Low-Power Process/Voltage/Temperature Monitor on 7nm

- The ODT-PVT-INT-001C-7 is an ultra-low power Temperature, Voltage and Process Monitor designed in a 7nm CMOS process.

- This IP operates over the entire temperature range of -40°C to 125°C.

- The Temperature Monitor (TM) achieves ±4°C temperature accuracy without trim and ±1°C temperature accuracy after a single room temperature trim.

-

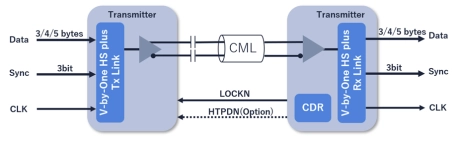

V-by-One® HS plus Tx/Rx IP

- IP core for FPGAs that supports “V-by-One® HS plus Standard”, the next-generation high-speed interface standard technology developed by THine Electronics Inc.

- V-by-One® HS plus Tx/Rx IP is an IP to enable Altera® FPGAs to send and receive signals compatible with the latest “V-by-One® HS plus Standard”.

-

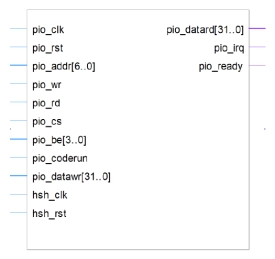

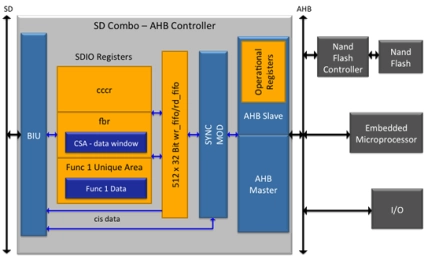

SD Card / SDIO Card Combo Device IP

- SD / SDIO Card Combo Device IP core is SD memory controller and a SDIO controller with an AHB interface.

- Combining with the optional NAND Flash Controller IP, the SD/SDIO Combo Device IP provides an integrated SD memory Card solution for designs that utilize NAND flash memory.

-

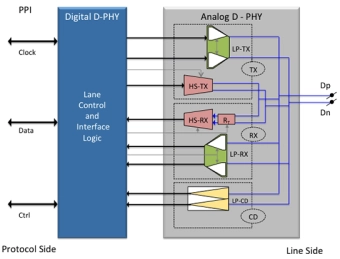

MIPI D-PHY Analog Transceiver IP Core

- The MIPI D-PHY Analog Transceiver IP Core is fully compliant with the D-PHY specification version 1.1.

- It supports the MIPI® Camera Serial Interface (CSI-2) and Display Serial Interface (DSI) protocols at speeds up to 1.5Gbps per lane.

- It is a Universal PHY that can be configured as a transmitter, receiver, or transceiver.

-

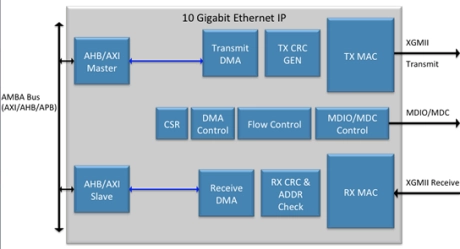

10 Gigabit Ethernet MAC IP Core

- The 10 Gigabit Ethernet (XGMAC) IP core is compliant with the Ethernet IEEE 802.3-2008 standard and provides an interface between AHB/AXI Bus and the 10 Gigabit Media Independent Interface (XGMII) using a powerful 64-bit Scatter Gather DMA.

- The 10 Gigabit Ethernet IP core is designed for applications such as integrated networking devices, host bus adapters, PCI-Express Ethernet controllers, and Ethernet adapter cards.

-

Standard Cell Libraries GF 55nm

- The Standard Cell libraries deliver thousands of highly optimized cells with each one being optimized for power, area, speed, routing, and yield.

- These libraries may be extended with Power Management Kits, taking power reduction to the next level, and ECO Kits to enable late-stage design modifications.

-

LPDDR5 IP solution

- Support LPDDR5 up to 6400Mbps

- Support Channel equalization with 1-tap DFE

- Support single-ended mode on CK, WCK and read DQS below 3200Mbps

- Support Link ECC for RDQS and DM

-

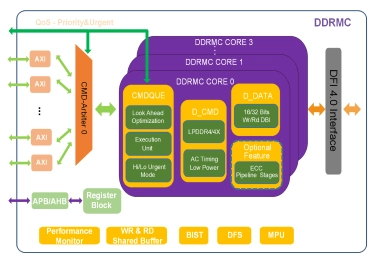

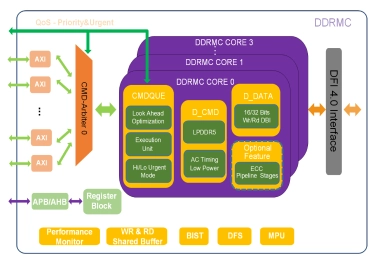

LPDDR4/4x IP solution

- Compatible with LPDDR4/4x up to 3733Mbps

- AXI compliant multi-ports, and data width, FIFO depth, command queue depth configurable

- DFI compliant interface between controller and PHY

- Support ECC (error correcting code)