Samsung 28nm FDSOI IP

Filter

Compare

16

IP

from

3

vendors

(1

-

10)

-

USB3.0 PHY on GF22FDX and Samsung 28nm FDSOI

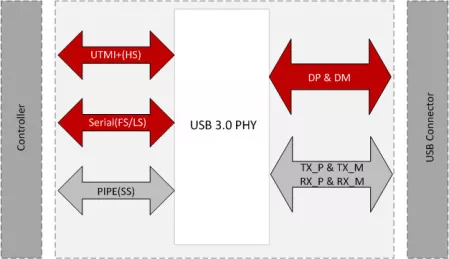

- The USB3.0 PHY IP is designed according to the USB 3.0, USB2.0 Specification.

- It supports the USB3.0 5Gbps Super-Speed mode and backward compatibles with the USB2.0 480Mbps High-Speed, 12Mbps Full-Speed, and 1.5Mbps Low-Speed modes

- The USB 3.0 PHY interface complies with PHY Interface for PCI Express and USB3.0 Architectures specification (PIPE 3.0) and the USB2.0 PHY interface complies with the UTMI v1.05 specification.

-

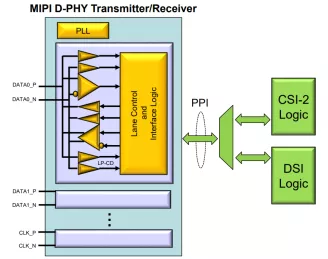

MIPI D-PHY Transmitter/Receiver for DSI/CSI-2 on Samsung 28nm FD-SOI

- Technology is Samsung 28nm FD-SOI 8M (6U1x_2T8x_LB).

- Supply voltage can be applied 1.1V for core voltage, 1.8V for IO voltage.

- Maximum data rate of each channel is 1.5Gbps at High-speed mode.

-

Samsung 28nm FDSOI MIPI DPHY V1.1

- Process: Samsung FDSOI 28nm 0.9V/1.8V, metal option TBD.

- Compliant to the MIPI D-PHY spec v1.1

- Data rate per lane: High-Speed mode 80M~1.5G bps, Low-Power mode 10Mbps

- Lane type:1 clock + 2 data, bi-directional

-

Samsung 28nm FDSOI 1.8v/1.0v LVDS Transmitter

- Process: Samsung 28nm FDSOI process

- Supply voltage: 2.25V<=VDD25<=2.75V, 0.9V<=VDD10<=1.1V 1.62V<=VDD18<=1.98v

- Mos device: pfet, nfet, egpfet, egnfet, rpposab

- Operating current:VDD25<24mA

-

Samsung 28nm FDSOI 1.8v/1.0v sub-LVDS Receiver

- Process: Samsung 28nm FDSOI process (0.9V / 1.8V)

- Supply voltage: 1.62V<=AVDD18<=1.98V, 0.9V<=AVDD10(VDD10)<=1.1V

- Mos device: pfet, nfet, egpfet, egnfet

- Operating current:AVDD18<24mA AVDD10<2mA

-

Samsung 28nm FDSOI 1.8v/1.0v APLL

- Process: Samsung 28nm FDSOI 1.0v1.8v process

- Supply voltage: 1.62V<=AVDD<=1.98V, 0.9V<=DVDD(AVDD2)<=1.1V

- Mos device: pfet, nfet, egpfet, egnfet, vncap, rpposab

- Operating current:AVDD<4mA(2.4GHz)

-

Samsung 28nm FDSOI 1.8v/1.0v APLL

- Process: Samsug 28nm FDSOI 1V/1.8V CMOS process

- Supply voltage: 0.9V<=VDDA<=1.1V, 0.9V<=VDD<=1.1V

- Mos device type: nfet, pfet

-

Samsung 28nm FDSOI 1.8v/1.0v APLL

- Process: Samsug 28nm FDSOI 1V/1.8V CMOS process

- Supply voltage: 0.9V<=VDDA<=1.1V, 0.9V<=VDD<=1.1V

-

Samsung 28nm FDSOI USB3.0 and PCIE2 combo PHY

- USB3.0 Super-Speed: Universal Serial Bus 3.0 Specification, Revision 1.0

- PCI Express: PCI Express Base Specification, Revision 2.0

-

Samsung 28nm FDSOI USB3.0 Type-C PHY

- 5-Gbps Super-Speed data transmission rate through 3-m USB3.0 cable

- Spread Spectrum clock (SSC) and data scrambling to minimize EMI

- PIPE 3-compliant Super-Speed USB 3.0 Transceiver interface

- Supports 16-bit 250-MHz , and 32-bit 125M PIPE interface