SLVS-EC Interface IP

Filter

Compare

15

IP

from

4

vendors

(1

-

10)

-

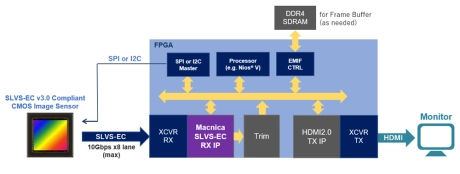

SLVS-EC RX PHY IP

- Fully compliant with SLVS-EC v3.0 specification.

- Supports both synchronous and asynchronous clocking.

- Up to 10Gbps per lane with 40-bit parallel data bus.

- Maximum output clock frequency of 250MHz.

-

-

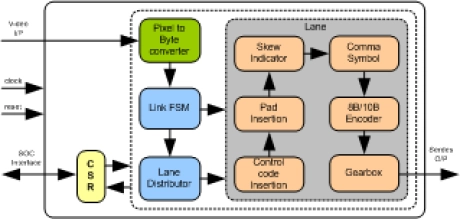

SLVS-EC TRANSMITTER IIP

- Compliant with SLVS-EC specification 2.0.

- Full SLVS-EC transmit functionality.

- Supports the following system topologies between CIS and DSP

- Basic Topology

-

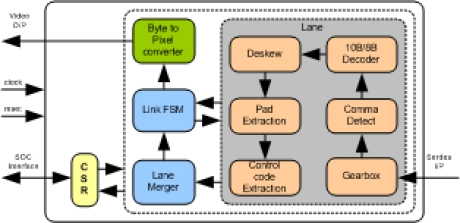

SLVS-EC RECEIVER IIP

- Compliant with SLVS-EC specification 2.0.

- Full SLVS-EC receive functionality.

- Compatible with following system topologies between CIS and DSP

- Basic Topology

-

SLVS-EC Receiver IP

- SLVS-EC is the next-generation, high-speed interface for high-resolution CMOS image sensors.

- This standard is tolerant of lane-to-lane skew because of embedded clock technology that simplifies board-level design of high-speed and long-distance data transmission.

-

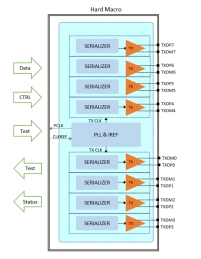

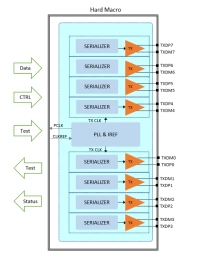

SLVS-EC TX PHY - 10GBPS 8-Lane - TSMC 12FFC

- SLVS-EC ver.3.0 compliant

- Data Rate: Up to 10Gbps / lane

- Number of data lane: 8

- Support input clock: 24MHz, 54MHz, 37.125MHz, 72MHz, 74.25MHz

-

Camera Receiver - 10.0Gbps 8-Lane - TSMC 12FFC

- The CL12812M8RIP10000 is an ideal means to link Camera Modules or CMOS Image Sensor (CIS) to ISP (Imaging Signal Processor) and DSP.

- The CL12812M8RIP10000 is designed to support data rate in excess of maximum 10Gbps utilizing SLVS-EC ver.3.0 interface specification.

-

Camera Receiver - 5.0Gbps 8-Lane - TSMC 12FFC, 6FFC

- The CL12812M8RIP5000 is an ideal means to link Camera Modules or CMOS Image Sensor (CIS) to ISP (Imaging Signal Processor) and DSP.

- The CL12812M8RIP5000 is designed to support data rate in excess of maximum 5Gbps utilizing SLVS-EC ver.3.0 BG3 interface specification

-

Camera Combo Receiver - 2.4Gbps 8-Lane - TSMC 28nm HPC

- The CL12832M8R2JM3KIP2400 is designed to support data rate in excess of maximum 2.4Gbps utilizing SLVS-EC / sub-LVDS / CMOS 1.8V interface specification.

- The CL12832M8R2JM3KIP2400 can change Interface type to same PAD for changing mode.

-

Multi-PHY Receiver Link Controller

- CD12842M8LRM3BM4AIP312P5 is a link IP that allows you to link a camera module or CMOS image sensor (CIS) to a host system.

- This LINK IP is a soft macro IP that has the function of converting MIPI CSI2 protocol or other interface protocol to the data for application layer.